## NORTHEASTERN UNIVERSITY

## Graduate School of Engineering

| Thesis Title:   | Memory Architecture for Data Intensive Image Processing Algorithms in Reconfigurable Hardware |                             |  |

|-----------------|-----------------------------------------------------------------------------------------------|-----------------------------|--|

| Author: Haiq    | ian Yu                                                                                        |                             |  |

| Department:     | Electrical and Compute                                                                        | r Engineering               |  |

| Approved for    | Thesis Requirement of th                                                                      | ne Master of Science Degree |  |

| Thesis Adviso   | r: Prof. Miriam Leeser                                                                        | Date                        |  |

| Thesis Reader   | : Prof. Eric Miller                                                                           | Date                        |  |

| Thesis Reader   | : Prof. Jennifer Dy                                                                           | Date                        |  |

| Department Cl   | hair: Prof. Fabrizio Lomb                                                                     | pardi Date                  |  |

| Graduate Scho   | ool Notified of Acceptanc                                                                     | ce:                         |  |

| Director of the | Graduate School                                                                               | Date                        |  |

## NORTHEASTERN UNIVERSITY

Graduate School of Engineering

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Memory Architecture for Data Intensive Image Processing Algorithms in<br>Reconfigurable Hardware |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|

| Author: Haiqian Yu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                  |  |  |

| <b>Department:</b> Electrical and Compute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | er Engineering                                                                                   |  |  |

| Approved for Thesis Requirement of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ne Master of Science Degree                                                                      |  |  |

| The state of the s |                                                                                                  |  |  |

| Thesis Advisor: Prof. Miriam Leeser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Date                                                                                             |  |  |

| Thesis Reader: Prof. Eric Miller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Date                                                                                             |  |  |

| Thesis Reader: Prof. Jennifer Dy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Date                                                                                             |  |  |

| Department Chair: Prof. Fabrizio Lomb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | pardi Date                                                                                       |  |  |

| Graduate School Notified of Acceptance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ce:                                                                                              |  |  |

| Director of the Graduate School                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Date                                                                                             |  |  |

| Copy Deposited in Library:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                  |  |  |

| Reference Librarian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Date                                                                                             |  |  |

# MEMORY ARCHITECTURE FOR DATA INTENSIVE IMAGE PROCESSING ALGORITHMS IN RECONFIGURABLE HARDWARE

A Thesis Presented

by

Haiqian Yu

to

The Department of Electrical and Computer Engineering

in partial fulfillment of the requirements

for the degree of

**Master of Science**

in

**Electrical Engineering**

in the field of

Electrical Engineering

Northeastern University

Boston, Massachusetts

August 2003

## Acknowledgements

First, I would like to thank my advisor Prof. Miriam Leeser for her consistent support and patient guidance throughout this project. I benefit a lot from Prof. Miriam Leeser's keen insight of complicated problems and her useful suggestions.

Many thanks should go to Mercury Computer Systems Inc., which initiated the project and funded my research. During the past two years, they provided useful information and constructive suggestions that is essential for this thesis.

I would also like to thank my colleagues from the Rapid Prototyping Group at Northeastern University for creating encouraging and supportive academic atmosphere that makes research work more enjoyable.

Thanks to Srdjan Coric for allowing me to use "Parallel-beam Filterd Backprojection" section from his thesis.

A special thanks goes to my husband, my parents and my sisters for their unconditional love and constant encouragement. Their true love has been and will be the stimulus for my whole life.

## **Abstract**

FPGA implementation is attractive for computationally-intensive applications due to FPGA's speed and flexibility. Many of these applications, including image processing, are data-intensive at the same time. In most cases, off-chip memory banks have to be used to store the large amounts of data. Memory architecture organization then becomes critical for an optimized design since frequent memory accesses can result in long delays and degrade the system performance. A two-stage memory access structure, which utilizes *locality of reference* has proved to be a successful implementation. In this research, we apply this structure to the backprojection application. The idea of this expandable architecture can be generalized to apply to other data-intensive applications.

An adaptive module is used in our implementation to isolate the core design and the memory interface. This extra module can greatly improve the re-use of the HDL code when migrating the design to a different hardware platform. Our implementation results show that the hardware system can work on different target FPGA computing boards with only a little modification. Moreover, performance is not affected on our current platform, we can achieve more than 100 times speedup over software implementation.

## **Contents**

| Acknowledgements                                     | 1  |

|------------------------------------------------------|----|

| Abstract                                             | 2  |

| Contents                                             | 3  |

| List of Figures                                      | 5  |

| List of Tables                                       | 6  |

| 1 Introduction                                       | 7  |

| 1.1 Thesis Outline                                   | 8  |

| 2 Background                                         | 10 |

| 2.1 Algorithm Introduction                           | 10 |

| 2.1.1 Parallel-beam Filtered Backprojection          | 10 |

| 2.1.2 Adapted Algorithm with Hardware Considerations | 19 |

| 2.2 HDL Based FPGA Design Process                    | 20 |

| 2.2.1 Hardware Description Languages                 | 20 |

| 2.2.2 FPGA Design Flow                               | 22 |

| 2.2.3 FPGA Structure and On-chip Memory              | 23 |

| 2.3 Computing Boards                                 | 27 |

| 2.4 Related Work                                     | 30 |

| 2.5 Summary                                          | 33 |

| 3 Experiment setup                                   | 34 |

| 3.1 Bit-width Selection                              | 34 |

| 3.2 Memory Architecture                              | 35 |

| 3.3 Simple Architecture                              | 40 |

| 3.4 Advanced Architecture                            | 43 |

| 3.4.1 WildStar                                          | 44 |

|---------------------------------------------------------|----|

| 3.4.2 FireBird                                          | 45 |

| 3.5 Adaptive Module                                     | 48 |

| The function of these three process is described below: | 54 |

| 3.6 Summary                                             | 55 |

| 4 Results and Performance                               | 56 |

| 4.1 Results                                             | 56 |

| 4.2 Performance                                         | 58 |

| 4.3 Summary                                             | 62 |

| 5 Conclusion and Future Work                            | 63 |

| 5.1 Conclusion                                          | 63 |

| 5.2 Future Work                                         | 64 |

| Bibliography                                            | 67 |

| Appendix A                                              | 70 |

## **List of Figures**

| Figure 2.1:  | Illustration of the coordinate system used in parallel-beam backprojection                     |

|--------------|------------------------------------------------------------------------------------------------|

| Figure 2.2:  | Reconstructions are often done using a procedure known as backprojection. Here a filtered      |

|              | projection is smeared back over the reconstruction plane along lines of constant t. (From      |

|              | [2].)                                                                                          |

| Figure 2.3:  | The ideal filter response for the filtered backprojection algorithm is shown here. It has been |

|              | bandlimited to $1/(2\tau)$ . (From [2].)                                                       |

| Figure 2.4:  | The impulse response of the filter shown in Fig. 2.3 is shown here. (From [2].)                |

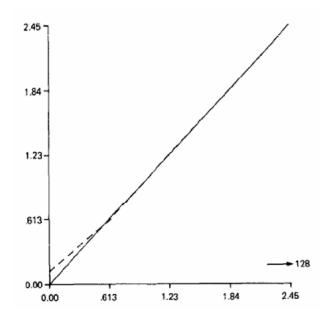

| Figure 2.5:  | The DFT of the bandlimited filter (broken line) and that of the ideal filter solid line) are   |

|              | shown here. Notice the primary difference is in the dc component. (From [2].)                  |

| Figure 2.6:  | HDL-based FPGA design flow                                                                     |

| Figure 2.7:  | FPGA structure                                                                                 |

| Figure 2.8:  | 2-Slice Virtex CLB (From Xilinx, Inc.)                                                         |

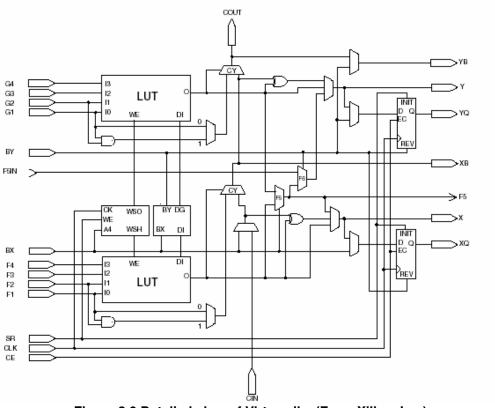

| Figure 2.9:  | Detailed view of Virtex slice(From Xilinx, Inc.)                                               |

| Figure 2.10: | Annapolis WildStar (From Annapolis Micro Systems, Inc.)                                        |

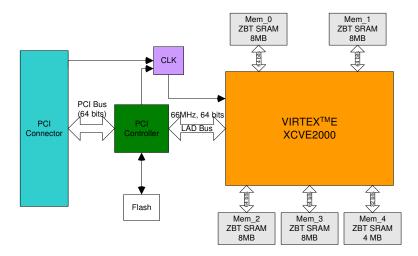

| Figure 2.11: | Annapolis FireBird (From Annapolis Micro Systems, Inc.)                                        |

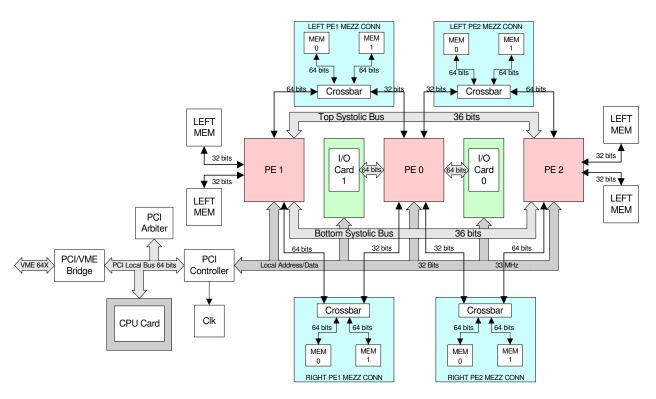

| Figure 2.12: | WildStar Schematic Diagram (From Annapolis Micro Systems, Inc.)                                |

| Figure 2.13: | FireBird Schematic Diagram (From Annapolis Micro Systems, Inc.)                                |

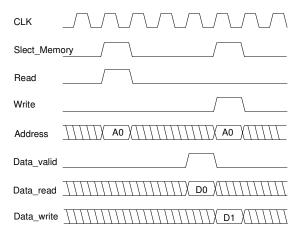

| Figure 3.1:  | Typical memory read                                                                            |

| Figure 3.2:  | Typical memory read-and-write                                                                  |

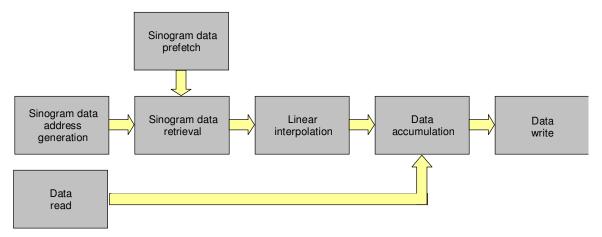

| Figure 3.3:  | Data flow diagram in parallel-beam backprojection                                              |

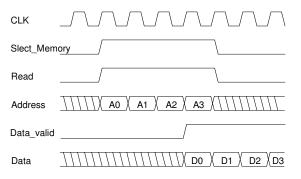

| Figure 3.4:  | Typical synchronized memory read                                                               |

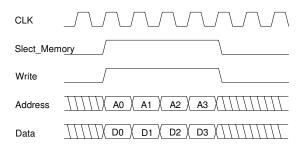

| Figure 3.5:  | Typical synchronized memory write                                                              |

| Figure 3.6:  | Hardware Structure                                                                             |

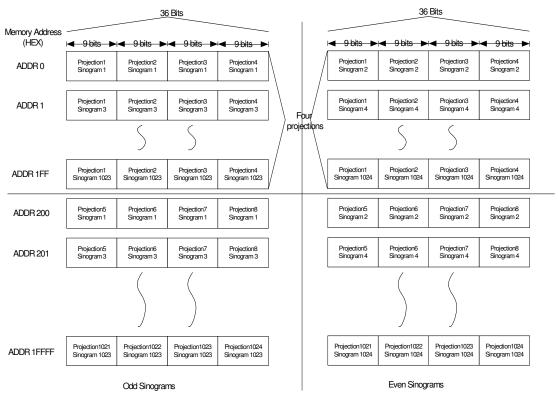

| Figure 3.7:  | Data format in off-chip memory                                                                 |

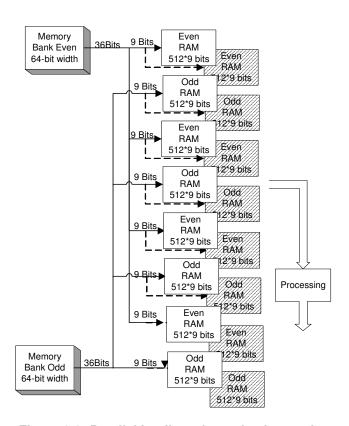

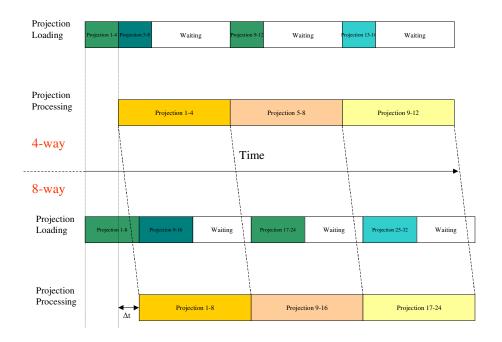

| Figure 3.8:  | Parallel loading of 4 projections using two input                                              |

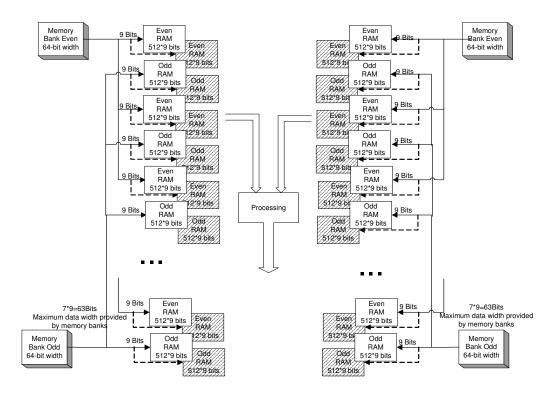

| Figure 3.9:  | Parallel loading 14 projections using four input                                               |

| Figure 3.10: | Extending the loading time                                                                     |

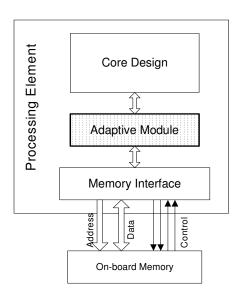

| Figure 3.11: | Interface adaptive module                                                                      |

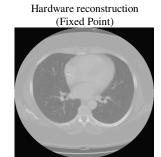

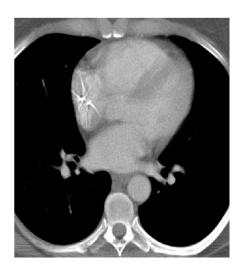

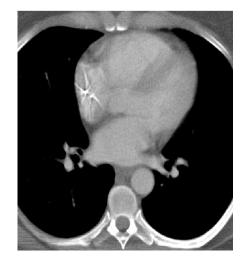

| Figure 4.1:  | Reconstructed image comparison                                                                 |

| Figure 4.2:  | Reconstructed image comparison, enlarged                                                       |

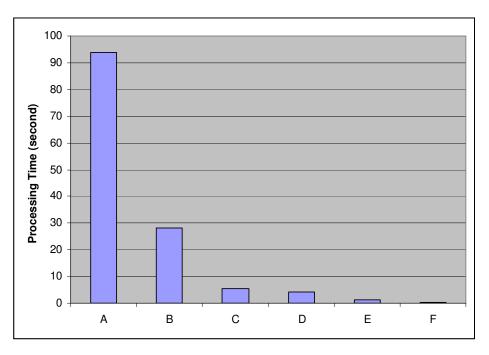

Figure 4.3: Processing time comparison

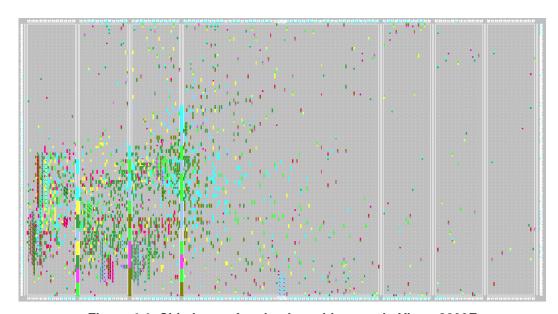

Figure 4.4: Chip layout for simple architecture in Virtex 2000E

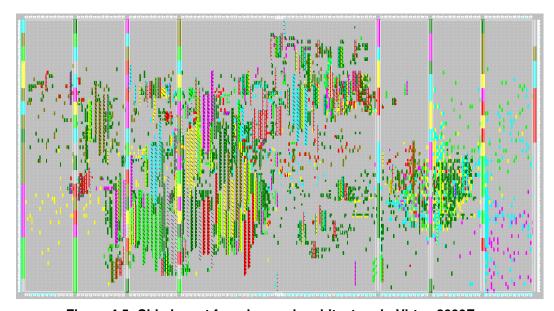

Figure 4.5: Chip layout for advanced architecture in Virtex 2000E

## **List of Tables**

Table 2.1: FPGA block RAM depth and width aspect ratios

Table 2.2: WildStar and FireBird Specifications

Table 3.1: WildStar and FireBird Specifications

Table 3.2: Resource Usage for Simple Architecture

Table 3.3: Resource Usage for Advanced Architecture

Table 3.4: WildStar and FireBird handshaking signals

Table 4.1: Speed-up Performance

## Chapter 1

## Introduction

Computer images are extremely data intensive and hence require large amounts of memory for storage. Image processing, in most cases, is data intensive as well as computation intensive. To provide the horsepower necessary to process large amounts of data in real-time, general-purpose DSP processors boards, application specific integrated circuits (ASICs), multiprocessing systems and filed programmable gate arrays (FPGAs) have been chosen to accelerate the processing time. Among all these methods, reconfigurable devices are attractive due to their ability to be dynamically reconfigured for different application and their inherent fine-grained parallelism. Moreover, FPGAs provide a simpler design cycle than ASICs, which makes time to market shorter, and have greater customization capabilities to make hardware more efficient than a software solution.

Due to the limited memory resources and complexity of the routing architecture [1] on the FPGA chip, external memory banks are necessary for most image processing applications. This also means that part of the FPGA needs to be configured as an interface to the external memory while the other part is configured to perform the required image processing operation. In this thesis, we call these external memories off-chip memory, in contrast with block RAMs inside FPGA chip, which is called on-chip

memory. Normally off-chip memory, although much larger, has slower reads/writes than on-chip memory. Accelerating the processing time while utilizing the large storage space of off-chip memory heavily depends on how we design the memory architecture. In this thesis, using the parallel-beam backprojection algorithm [2] as an example, we discuss FPGA memory architectures for data intensive image processing applications.

Another issue for hardware design is its re-use. Due to the off-chip memory requirement, we have to design different memory interfaces for different target boards. Synchronization between computation and memory read/write are critical for the processing, thus some of the memory handshaking signals are used as control signals in the design. If we change the target board, we may have to rewrite most of the VHDL code. In this thesis, we present an adaptive module between the core design and the memory interface that can maximally isolate the two parts. In this case, when we migrate the design from one board to another, we only need to rewrite the adaptive module. This can greatly increase the re-usability of the VHDL code and correspondingly, shorten the time-to-market cycle.

#### 1.1 Thesis Outline

This thesis is organized as follows:

Chapter 2 describes the algorithm of parallel-beam backprojection followed by a brief review of the HDL-based FPGA design process. In this chapter, the FPGA

computing boards we used and their differences are also introduced. The final part gives an overview of related work. Chapter 3 describes the detailed hardware implementation process, specifically concentrating on the memory architecture design of both simple and advanced architectures for our design. The use of the adaptive module is also introduced in this chapter. Chapter 4 gives the results and analysis of the hardware design. The performance of two different implementations are included in this chapter. Chapter 5 presents conclusion and gives suggestions for future work.

## Chapter 2

## **Background**

Before addressing the memory organization issues in this thesis, we give some basic information on the parallel-beam backprojection algorithm. After that, a brief overview of reconfigurable hardware in general and specifics of the platform used for hardware implementation are described. Related work is also summarized in this chapter.

## 2.1 Algorithm Introduction

The most commonly used approach for image reconstruction from parallel-beam projection data is filtered backprojection. The following sections introduce the detailed algorithm and the corresponding hardware adapted algorithm. Most of this material has been presented previously in [2,3,4].

#### 2.1.1 Parallel-beam Filtered Backprojection

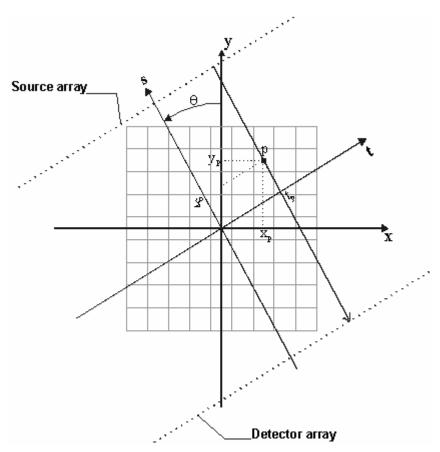

A parallel-beam CT scanning system uses an array of equally spaced unidirectional sources of focused X-ray beams. Generated radiation, not absorbed by the object's internal structure, reaches a collinear array of detectors (Figure 2.1). Spatial

variation of the absorbed energy in the two-dimensional plane through the object is expressed by the attenuation coefficient f(x, y). The logarithm of the measured radiation intensity is proportional to the integral of the attenuation coefficient along the straight

Figure 2.1: Illustration of the coordinate system used in parallel-beam backprojection

line traversed by the X-ray beam. A set of values given by all detectors in the array comprises a one-dimensional projection of the attenuation coefficient,  $P(t, \theta)$ , where t is the detector distance from the origin of the array, and  $\theta$  is the angle at which the measurement is taken. A collection of projections for different angles over  $180^{\circ}$  can be visualized in the form of an image in which one axis is position t and the other is angle  $\theta$ .

This is called a sinogram or Radon transform of the two-dimensional function f, and it contains information needed for the reconstruction of an image f(x, y). The Radon transform can be formulated as

$$\log_e \frac{I_0}{I_d} = \iint f(x, y) \delta(x \cos \theta + y \sin \theta - t) dx dy \equiv P(t, \theta), \qquad (2.1)$$

where  $I_o$  is the source intensity,  $I_d$  is the detected intensity, and  $\delta(\cdot)$  is the Dirac delta function. Equation (2.1) is actually a line integral along the path of the X-ray beam, which is perpendicular to the t axis (see Figure 2.1) at location  $t = x\cos\theta + y\sin\theta$ . The Radon transform represents an operator that maps an image f(x, y) to a sinogram  $P(t, \theta)$ . Its inverse mapping, called the inverse Radon transform, applied to a sinogram results in an image. The filtered backprojection (FBP) algorithm performs this mapping [2].

The mathematical derivation of the filtered backprojection algorithm for parallelbeam projections is summarized and presented in [3]. Here we directly give the final conclustion.

$$f(x, y) = \int_{0}^{\pi} Q_{\theta}(x \cos \theta + y \sin \theta) d\theta$$

(2.2)

where

$$Q_{\theta}(t) = \int_{-\infty}^{\infty} S_{\theta}(w) |w| e^{j2\pi wt} dw.$$

(2.3)

This estimate of f(x, y), given the projection data transform  $S_{\theta}(w)$ , has a simple form. Equation (2. 3) represents a filtering operation, where the frequency response of

the filter is given by |w|; therefore  $Q_{\theta}(t)$  is called a "filtered projection." The resulting projections for different angles  $\theta$  are then added to form the estimate of f(x, y).

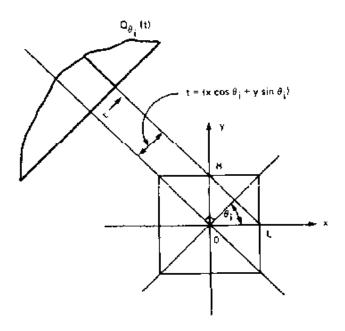

Equation (2.2) calls for each filtered projection,  $Q_{\theta}$ , to be "backprojected." This can be explained as follows. To every point (x, y) in the image plane there corresponds a value of  $t = x \cos \theta + y \sin \theta$  for a given value of  $\theta$ , and the filtered projection  $Q_{\theta}$  contributes to the reconstruction of its value at  $t = x \cos \theta + y \sin \theta$ .

Figure 2.2: Reconstructions are often done using a procedure known as backprojection. Here a filtered projection is smeared back over the reconstruction plane along lines of constant t. (From [2].)

This is further illustrated in Fig. 2.2. It is easily shown that for the indicated angle  $\theta$ , the value of t is the same for all (x, y) on the line LM. Therefore, the filtered projection,  $Q_{\theta}$ , will make the same contribution to the reconstruction at all of these

points. Therefore, one could say that in the reconstruction process each filtered projection,  $Q_{\theta}$ , is smeared back, or backprojected, over the image plane.

The parameter w has the dimension of spatial frequency. The integration in (2.3) must, in principle, be carried out over all spatial frequencies. In practice the energy contained in the Fourier transform components above a certain frequency is negligible, so for all practical purposes the projections may be considered to be band-limited. If W is a frequency higher than the highest frequency component in each projection, then by the sampling theorem the projections can be sampled at intervals of

$$T = \frac{1}{2W} \tag{2.4}$$

without introducing any error. If we also assume that the projection data are equal to zero for large values of |t| then a projection can be represented as

$$P_{\theta}(mT), \qquad m = \frac{-N}{2}, \dots, 0, \dots, \frac{N}{2} - 1$$

(2.5)

for some (large) value of *N*.

Assume that the projection data are sampled with a sampling interval of  $\tau$  cm. If there is no aliasing, then in the transform domain the projections don't contain any energy outside the frequency interval (- W, W) where

$$W = \frac{1}{2\tau} \text{ cycles/cm.}$$

(2.6)

Let the sampled projections be represented by  $P_{\theta}(k\tau)$  where k takes integer values. The theory presented in the preceding subsection says that for each sampled projection  $P_{\theta}(k\tau)$  we must generate a filtered  $Q_{\theta}(k\tau)$ . When the highest frequency in the projections is finite (as given by Eq. (2.6)), Eq. (2.3) may be expressed as

$$Q_{\theta}(t) = \int_{-\infty}^{\infty} S_{\theta}(w)H(w) e^{j2\pi wt} dw$$

(2.7)

where

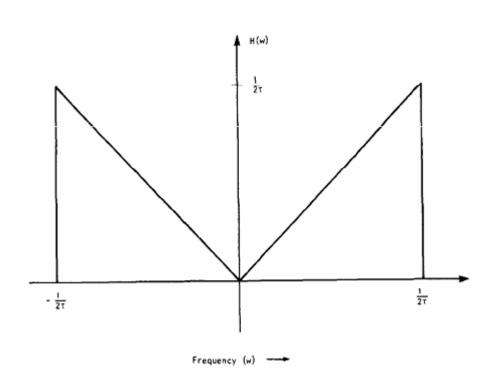

$$H(w) = |w| b_w(w) \tag{2.8}$$

where, again,

$$b_w(w) = \begin{cases} 1 & |w| < W \\ 0 & \text{otherwise} . \end{cases}$$

(2.9)

H(w), shown in Fig. 2.3, represents the transfer function of a filter with which the projections must be processed. The impulse response, h(t), of this filter is given by the inverse Fourier transform of H(w) and is

$$h(t) = \int_{-\infty}^{\infty} H(w) e^{j2\pi wt} dw$$

$$= \frac{1}{2\tau^2} \frac{\sin 2\pi t/2\tau}{2\pi t/2\tau} - \frac{1}{4\tau^2} \left(\frac{\sin \pi t/2\tau}{\pi t/2\tau}\right)^2$$

(2.10)

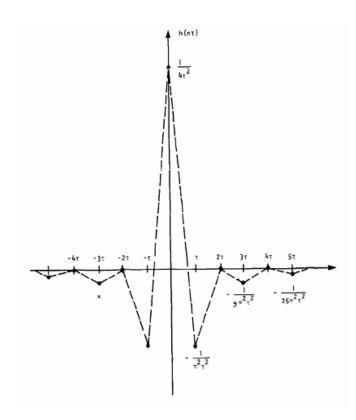

where we have used Eq. (2.6). Since the projection data are measured with a sampling interval of  $\tau$ , for digital processing the impulse response need only be known with the same sampling interval. The samples,  $h(n \tau)$ , of h(t) are given by

$$h(n\tau) = \begin{cases} \frac{1}{4\tau^2}, & n = 0\\ 0, & n \text{ even} \\ -\frac{1}{n^2\pi^2\tau^2} & n \text{ odd} \end{cases}$$

(2.11)

This function is shown in Fig. 2.4.

Figure 2.3: The ideal filter response for the filtered backprojection algorithm is shown here. It has been bandlimited to  $1/(2\tau)$ . (From [2].)

By the convolution theorem the filtered projection at the sampling points can be written as

$$Q_{\theta}(n\tau) = \tau \sum_{k=-\infty}^{\infty} h(n\tau - k\tau) P_{\theta}(k\tau). \qquad (2.12)$$

In practice each projection is of only finite extent. Suppose that each  $P_{\theta}(k\tau)$  is zero outside the index range  $k=0,\ldots,N-1$ . We may now write the following two equivalent forms of Eq. (2.12):

$$Q_{\theta}(n\tau) = \tau \sum_{k=0}^{N-1} h(n\tau - k\tau) P_{\theta}(k\tau), \quad n=0, 1, 2, ..., N-1$$

(2.13)

or

$$Q_{\theta}(n\tau) = \tau \sum_{k=-(N-1)}^{N-1} h(k\tau) P_{\theta}(n\tau - k\tau), \quad n=0, 1, 2, ..., N-1$$

(2.14)

Figure 2.4: The impulse response of the filter shown in Fig. 2.3 is shown here. (From [2].)

These equations imply that in order to determine  $P_{\theta}(k\tau)$  the length of the sequence  $h(n\tau)$  used should be from l = -(N-1) to I = (N-1). It is important to realize that the discrete Fourier transform of the sequence  $h(n\tau)$  with n taking values in a finite range [such as when n ranges from -(N-1) to (N-1)] has a nonzero dc component which is not the case for the ideal filter response. This is illustrated in Fig. 2.5.

Figure 2.5: The DFT of the bandlimited filter (broken line) and that of the ideal filter (solid line) are shown here. Notice the primary difference is in the dc component. (From [2].)

The reconstructed picture f(x, y) may then be obtained by the discrete approximation to the integral in Eq. (2.3), i.e.,

$$f(x, y) = \frac{\pi}{K} \sum_{i=1}^{K} Q_{\theta_i} \left( x \cos \theta_i + y \sin \theta_i \right), \tag{2.15}$$

where the K angles  $\theta_i$  are those for which the projections  $P_{\theta}(t)$  are known. Note that the value of  $x \cos \theta_i + y \sin \theta_i$  in Eq. (2.15) may not correspond to one of the  $k\tau$  at which  $Q_{\theta_i}$  is known. However,  $Q_{\theta_i}$  for such t may be approximated by suitable interpolation; often, linear interpolation is adequate.

#### 2.1.2 Adapted Algorithm with Hardware Considerations

For the practical implementation of filtered parallel-beam backprojection, it is important to determine how many projections and how many samples per projection one should use to obtain a highly accurate reconstruction. The values [3] used for our implementation, are: the reconstructed image size is 512\*512, the number of projections is 1024, each projection has 1024 samples. We also assume square pixels and use the look-up tables (LUTs) and incremental spatial address calculation as suggested in [4].

Basically, equation (2.15) can be summarized as follows: For each pixel of the reconstructed image, we should find the sinogram data that contributes to this pixel for the current projection and accumulate the value for all the projections.

According to the image size and sinogram size we select, the input of the design would be the 1024\*1024 sinogram data and the output is the 512\*512 reconstructed image. To get the output, the computation would be 512\*512\*1024 since reconstruction is an accumulation process through 1024 projections for each pixel. Clearly, this is both a computation-intensive and memory-intensive algorithm. For software calculation, it takes

minutes to hours for one image reconstruction depending on the software and the algorithm. Our fastest software implementation needs 28 seconds, which is too slow for real-time applications. That is one of the reasons why we designed a hardware implementation for acceleration. Xilinx FPGA chips are our target technology due to their flexibility and processing speed. However, using current technology, it is impossible to load all the input data or output data to any FPGA for computation. That means we have to use some external memory banks with interfaces to the FPGA chip to store the input and output data. For maximum performance, we have to carefully design the memory architecture, fully utilizing the pipelined structure and parallelism of the design.

## **2.2 HDL Based FPGA Design Process**

#### 2.2.1 Hardware Description Languages

HDLs provide formats for representing various design stages. They are used to describe hardware for the purpose of simulation, modeling, testing, design, and documentation. These languages provide a convenient and compact format for the hierarchical representation of functional and wiring details of digital systems. There are several levels of abstraction of digital systems using hardware description languages.

A *Behavioral description* is the most abstract. It describes the function of the design in a software-like procedural form and provides no detail as to how the design is to be implemented. Behavioral descriptions are necessary in the early design stage so that simulations can ensure that the chip is functionally correct. The advantage of this approach is that we can make this assessment independent of the many possible physical implementations.

A *dataflow description* is a concurrent representation of the flow of control and movement of data. It gives more detail of hardware implementation and shows how data moves between registers.

A *structural description* is the lowest and most detailed level of description considered here and is the simplest to synthesize into hardware.

Available software for HDLs includes simulators and hardware synthesis programs. A simulation program can be used for design verification, while a synthesizer is used for automatic hardware generation. Moreover, synthesizers can be divided into two parts, high level synthesizer and low level synthesizer. The high level synthesizer can transform behavioral description HDL into structural description HDL, which includes some primitive components, generally gates, flip-flops and latches. The low level synthesizer depends on the target hardware and its main tasks are place & route and optimization. In some papers and books, this process is called hardware implementation since the output of the low level synthesizer directly maps to the primitives that are used in the target chip.

## 2.2.2 FPGA Design Flow

Typically, the HDL-based FPGA design flow has three steps:

- 1. Use VHDL or Verilog to describe digital systems; a simulation tool is required to simulate and verify the design.

- 2. Use RTL (Register Transfer Level) synthesis tool to obtain structure level design.

- 3. Use FPGA placement & routing tools to obtain physical FPGA netlist.

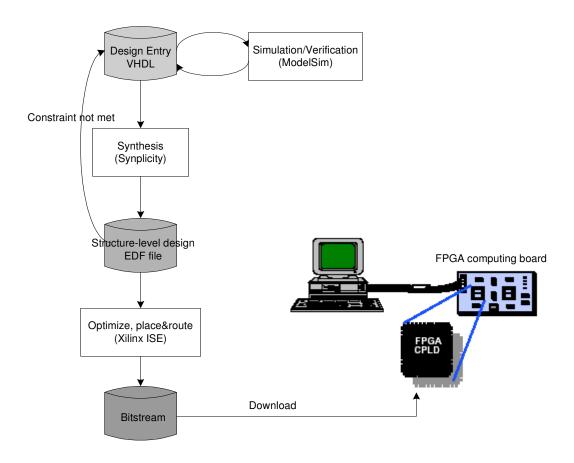

Figure 2.6 HDL-based FPGA design flow

Specifically, our FPGA design flow is shown in Figure 2.6.

ModelSim, Synplify and Xilinx ISE are the tools we used for simulation, synthesis and implementation respectively. The final bit-stream is downloaded to the FPGA computing board through a host PC. We check the output of our implementation for function verification. If the result is not correct, then we will go through the three steps again until we get the final successful design. The following section explains why we are using FPGA computing boards.

#### 2.2.3 FPGA Structure and On-chip Memory

The key to the popularity of FPGAs is their ability to implement any circuit simply by being appropriately programmed. Other circuit implementation options, such as Standard Cells or Mask-Programmed Gate Arrays (MPGAs), require that a different VLSI chip be newly fabricated for each design. The use of a standard FPGA, rather than these custom technologies, has two key benefits: lower non-recurring engineering (NRE) costs, and faster time-to-market.

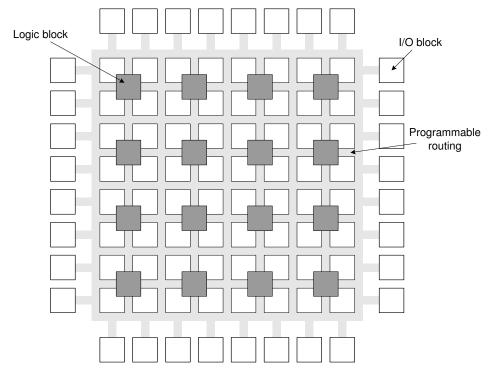

All FPGAs are composed of three fundamental components: logic blocks, I/O blocks and programmable routing, as Figure 2.7 shows. A circuit is implemented in an FPGA by programming each of the logic blocks to implement a small portion of the logic required by the circuit, and each of the I/O blocks to act as either an input pad or an output pad, as required by the circuit. The programmable routing is configured to make

all the necessary connections between logic blocks and from logic blocks to I/O blocks[1].

Figure 2.7 FPGA structure

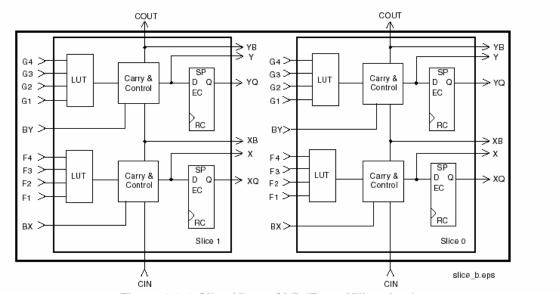

Figure 2.8 2-Slice Virtex CLB (From Xilinx, Inc.)

The logic block used in most modern FPGAs are composed of groups of Look-Up Tables and registers with some local interconnect between them. The FPGA chips we use are Xilinx Virtex series. Virtex devices provide better performance than previous generations of Xilinx FPGAs. Designs can achieve synchronous system clock rates up to 200MHz including I/O. Moreover, Virtex FPGAs incorporate several large block RAM memories. These complement the shallow RAM structures implemented in CLBs. For the Virtex series, each CLB contains four logic cells (LCs), organized in two similar slices, as shown in Figure 2.8. Figure 2.9 shows a more detailed view in a single slice [5,6]. These LUTs can either be combined or used separately to implement any logical function.

Figure 2.9 Detailed view of Virtex slice(From Xilinx, Inc.)

As we have mentioned before, FPGAs have two key benefits: lower non-recurring engineering (NRE) costs, and faster time-to-market. These two benefits make FPGAs one of the most popular implementation media for digital circuits.

Due to the memory requirement of most applications, most current FPGA chips, such as the Virtex, Spartan-3 and Virtex-II series, have several block RAMs inside the chips. We are interested in Virtex series since they are the FPGA chips we used currently. The following discussion about block RAMs are specific to Virtex series unless specified. Block RAMs are organized in columns and the number of block RAMs depends on the FPGA you choose. Each block RAM contains 4096 memory cells and provide true dual-read/write port synchronous RAM. Each port of the block RAM memory can be independently configured as a read/write port, a read port, or a write port; and each port can be configured to a specific data width such as 1,2,4,8.... That means if you use block RAM to store your 9 bit data, one block RAM can only store 256 data items since it has to select the 16-bit data width for storage. However, several block RAMs can be combined together to achieve wider and deeper RAM structures. Table 2.1 describes the depth and width aspect ratios for the block RAM. Another advantage of on-chip RAM is its short response time. Users can read/write data in one clock cycle.

For applications like image processing, which require a very large memory to store the data, it is impossible to load all the data into the FPGA block RAM due to its area and routing limitations. In our case, the input data is  $1024*1024*9bit \cong 1.1Mbyte$ , while the block RAMs in FPGA holds up to several hundred Kbytes.

Table 2.1 FPGA block RAM depth and width aspect ratios

| Width | Depth | ADDR Bus    | Data Bus   |

|-------|-------|-------------|------------|

| 1     | 4007  | ADDD :11.0: | DATEA (O)  |

|       | 4096  | ADDR<11:0>  | DATA<0>    |

| 2     | 2048  | ADDR<10:0>  | DATA<1:0>  |

| 4     | 1024  | ADDR<9:0>   | DATA<3:0>  |

| 8     | 512   | ADDR<8:0>   | DATA<7:0>  |

| 16    | 256   | ADDR<7:0>   | DATA<15:0> |

## **2.3 Computing Boards**

One of the biggest advantages of applying hardware designs to an FPGA is the possibility for really fast prototyping. However, although the turn around time from VHDL description to FPGA floorplan is short, the last step from having the floorplan to a working design in hardware can require an unintended percentage of the designers time schedule. The problem is that although the FPGA can function almost as a stand-alone unit; peripheral components, such as static memory and communication equipment usually have to be wired to the FPGA before such architectures can be verified. That is why we are using Annapolis Micro Systems' computing boards for our implementation. WildStar and FireBird [7,8] are two computing FPGA boards, which not only have large

off-chip memory storage, but also have PCI controllers. They make the data transfer between PC and the computing board very convenient. The manufacturer also provides user supplied interface code specific to the memory types, which define the handshaking signals between FPGA chip and memories. Users only need to use these signals to control the data exchange.

WildStar and FireBird's specifications are listed in Table 2.2:

Table 2.2 WildStar and FireBird Specifications

| WildStar                              | FireBird                                             |

|---------------------------------------|------------------------------------------------------|

| ■ 3 Xilinx® VIRTEX™ 1000 FPGAs with 3 | ■ 1 Virtex <sup>TM</sup> E FPGA Processing Element - |

| million system gates                  | XCV2000E, that is 2 million gates                    |

| Processing clock rates up to 100MHz   | Processing clock rates up to 150MHz                  |

| 1.6 GB/s I/O bandwidth                | 4.2 GB/s I/O bandwidth                               |

| 6.4 GB/s memory bandwidth             | 6.6 GB/s memory bandwidth                            |

| 40MB of 100MHz Synchronous ZBT SRAM   | 30MB of 150MHz Synchronous ZBT SRAM                  |

The pictures of these two boards and their schematic diagrams of the boards are shown in the following figures.

Figure 2.10: Annapolis WildStar (From Annapolis Micro Systems, Inc.)

Figure 2.11: Annapolis FireBird (From Annapolis Micro Systems, Inc.)

Figure 2.12: WildStar Schematic Diagram (From Annapolis Micro Systems, Inc.)

Figure 2.13: FireBird Schematic Diagram (From Annapolis Micro Systems, Inc.)

We have to divide the FPGA design into two parts; one is the processing part, which takes the data and does the processing, and the other is the memory interface, which reads/writes data from/to the memory. For memory-intensive designs like parallel-beam backprojection, we have to carefully organize the memory architecture for fast and efficient data exchange.

#### 2.4 Related Work

In previous work in the area of hardware implementations of tomographic processing algorithms, Wu[9] gives a brief overview of all major subsystems in a computed tomography (CT) scanner and proposes locations where ASICs and FPGAs can be utilized. According to the author's discussion, semi-custom digital ASICs were the

most appropriate due to the level of sophistication that FPGA technology had in 1991. Agi et. al.[10] present the first description of a hardware solution for computerized tomography of which we are aware. It is a unified architecture that implements forward Radon transform, parallel- and fan-beam backprojection in an ASIC based multiprocessor system. Our FPGA implementation focuses on backprojection. Agi et al. [11] present a similar investigation of quantization effects; however their results do not demonstrate the suitability of their implementation for medical applications. Although their filtered sinogram data are quantized with 12-bit precision, extensive bit truncation on functional unit outputs and low accuracy of the interpolation factor (absolute error of up to 2) render this implementation significantly less accurate than ours, which is based on 9-bit projections and the maximal interpolation factor absolute error of 2<sup>-4</sup>. An alternative to using specially designed processors for the implementation of filtered backprojection (FBP) is presented in [12]. In this work, a fast and direct FBP algorithm is implemented using texture-mapping hardware. It can perform parallel-beam backprojection of a 512-by-512-pixel image from 804 projections in 2.1 seconds, while our implementation takes 0.25 seconds from 1024 projections. Luiz et. al.[13] investigated residue number systems (RNS) for the implementation of convolution based backprojection to speedup the processing. Unfortunately, extra binary-to-RNS and RNSto-binary conversions are introduced. Approaches to accelerating the backprojection algorithm can be found in [14,15]. However, their suitability to medical image quality and hardware implementation are still under investigation. Bins et. al.[16] have

investigated precision vs. error in JPEG compression. The goals of this research are very similar to ours: to implement designs in fixed-point in order to maximize parallelism and area utilization. However, JPEG compression is an application that can tolerate a great deal more error than medical imaging.

In this thesis, we focus on FPGA implementation performance and medical image quality as well as the memory structure design for data-intensive applications. Filtered Back-Projection (FBP) is a computationally and data intensive process. For an image of size  $n \times n$  being reconstructed with n projections, the complexity of the backprojection algorithm is  $O(n^3)$ . The input data is  $n^2$  and the output data is also  $n^2$ . Moreover, a difficulty of implementing FBP is that producing high-resolution images with good resemblance to internal characteristics of the scanned object requires that both the density of each projection and their total number be large. This represents a considerable challenge for hardware implementations, which attempt to maximize the parallelism in the implementation. Therefore, it can be beneficial to use fixed-point implementations and to optimize the bit-width of a projection sample to the specific needs of the targeted application domain. In a previous thesis[3,4], the author presents a detailed hardware architecture based on software simulation results and successfully implements this application. Our FPGA design is based on these results [3,4] and pays more attention to the memory architecture organization.

Notably, problems arise when we migrating the backprojection design from one board to another. Ideally, once we get a successful HDL version of an FPGA design, we

expect it to work properly on other platforms without many modifications. Unfortunately, this seldom is the case for designs with interfaces to off-chip memories and/or I/O ports. Changes to the memory organization or board design may result in the designer having to rewrite most of the HDL code. This is the case when we migrated the memory-intensive design, parallel-beam backprojection, from the WildStar to FireBird boards from Annapolis Microsystems [7,8].

A lot of attention has been paid to building general-purpose memory interfaces to interact with external memory. Most of them aim at multi-processor FPGA systems [17,18] and are concerned with memory access conflict issues. For memory-intensive single processor FPGA designs with a vendor-specific HDL interface, we are more interested in a portable design with maximally re-use of the existing HDL code. Not much work has been done in this area.

### 2.5 Summary

This chapter gives the general background to the backprojection algorithm and the FPGA implementation of this algorithm. Our design entry and the design process are also introduced in this chapter. We emphasize on the on-chip and off-chip memory. Related work is also included here. We will discuss the memory issue in the next chapter.

# Chapter 3

## **Experiment setup**

The most important reason for hardware implementation is its higher processing speed. Fixed-point and pipelined structures are used in our implementation for speed-up. For an application with frequent memory accesses, a two-stage memory architecture is designed for further speed-up. Moreover, to maximize the re-use of our HDL-based design, we introduced an adaptive module in this thesis. This chapter gives the details of all these techniques we used in our design.

#### 3.1 Bit-width Selection

Unlike software computation, in hardware implementation fixed-point is preferred for its compact size and fast speed. Hardware size and speed are two primary factors for a high performance system. Smaller size means lower cost while higher speed means less processing time. When implementing an algorithm or application in hardware, normally we want to maximize the processing performance and keep the cost under some specified limit. For medical imaging, we have to take one more thing into consideration: accuracy.

Specifically, care must be taken so that very little error is introduced compared to floating-point implementations and the visual quality of the image is not compromised. That means when we reduce the bit-width to decrease the hardware size, we have to make sure the quality of the reconstructed image is comparable to the floating-point reconstruction. It is very important to balance area and accuracy. Larger bit width corresponds to more accuracy but also more area and lower speed. Moreover, we need to investigate for each stage of the design whether it is feasible to disregard some of the least significant bits (LSBs) and still not introduce any visible error.

According to simulation results from [3], which investigates the quantization effect for each stage of reconstruction, we use 9 bits for sinogram quantization and 3 bits for linear interpolation. Since disregarding LSBs won't save much hardware area, we preserve the LSBs for intermediate results at each stage. Pipelined structures are used for higher throughput.

## 3.2 Memory Architecture

As we have mentioned in the algorithm introduction, we reconstruct the image once for each projection and accumulate the results for all the projections. For each pixel, we need to find the address of the corresponding sinogram data that contributes to this pixel. We can't predict the address of the sinogram for the next pixel since it varies from

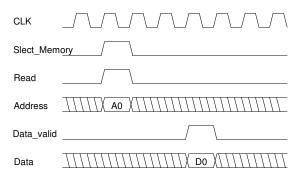

pixel to pixel, line to line, projection to projection. This is the issue: although we can easily access the on-chip memory in one clock cycle, the size of the on-chip memory is too small to store all the sinogram data. But if all the data are stored in off-chip memory, when the address is generated, we must send a read request to the memory, then wait for the data to be ready to read, which may take several cycles. In this case, even if we already have the next address, we can't get the data for several cycles. A typical memory read waveform is shown in Figure 3.1.

There is also not enough space for the reconstructed image in the on-chip

Figure 3.1: Typical memory read

Figure 3.2: Typical memory read-and-write

memory. For each projection, each pixel should be updated. That means it needs to be read in, the new value needs to be added and then the pixel should be stored back to the off-chip memory. This is a typical read-and-write cycle; its waveform is shown in Figure 3.2.

Clearly, if we want to update the image, we have to wait several clocks for each pixel. For example, if the number of clock cycles to wait for a read is 2, then for one projection, 512\*512\*2 clock cycles are wasted. For a processing frequency of 50MHz, the overall reconstruction will at least waste 512\*512\*2\*1024\*(1/50,000,000) = 10.737seconds. This will severely degrade performance.

In summary, if all the data are store in off-chip memory, we will waste a lot of time waiting for the data. On-chip memory has a much faster read/write cycle, but it cannot accommodate all the data. To solve this problem, we use a memory hierarchy structure in our design by exploiting the spatial locality of input data of the algorithm.

We already know that the sinogram address for the next pixel can not be determined by the current address, but if we have all the sinogram data for this projection stored in the block RAM, then we can always get the data no matter what the address is. That is spatial locality, which means that although we don't know which sinogram data will be selected for the next pixel, we do know it must be some of the data in the current projection. Based on this fact, we have the data flow shown in Figure 3.3.

Figure 3.3: Data flow diagram in parallel-beam backprojection

All the sinogram data for the first projection are pre-loaded to the on-chip memory. Once it is loaded, the sinogram data address generation (SAG) module starts to work. For each pixel to be reconstructed, the SAG finds out which sinogram value corresponds to this pixel for this projection. Linear interpolation is used in case the address is not an integer. All the calculations are pipelined for speedup. While the SAG is calculating the address for the current projection, the sinogram data for the next projection is preloaded in parallel. By this means, we only need to wait for the first projection to load. Once the first projection reconstruction is finished, we can immediately start the second round reconstruction. Moreover, since the sinogram data is loaded in the on-chip memory, we can get the data one clock cycle after we have the address information. We don't need to wait the extra clock cycles for the data to be valid from off-chip memory.

Extra memory banks are needed to store the output data, which represents the reconstructed image, since it is also too large to store in the on-chip memory. As

mentioned in chapter 2, for each projection, every pixel of reconstructed image needs to be updated. That means the output data does not exhibit spatial locality so we cannot use the same strategy as used for input memory. If we use only one off-chip memory as output memory, then as we have discussed before, if each pixel update needs 2 cycles, then the time for updating would be 10.737 sec with a 50MHz processing rate. That is definitely not what we want. Our solution is to use two output memories instead of one output memory. Since the reconstruction is accumulated for all the projections, we store the reconstructed image in one off-chip memory. Once the current reconstructed pixel value is calculated, it is added to the accumulated value from previous projections and store to another memory. Next time, these two memories change roles. By using this extra output memory, we can take advantage of the synchronized memory read/write and get one data value per cycle throughput. Timing diagrams for synchronized read and write are shown in Figures 3.4 and 3.5.

Figure 3.4: Typical synchronized memory read

Figure 3.5: Typical synchronized memory write

Synchronization is critical for this part because when accumulating, the computing pipeline and the data read from memory must correspond to the same pixel.

## 3.3 Simple Architecture

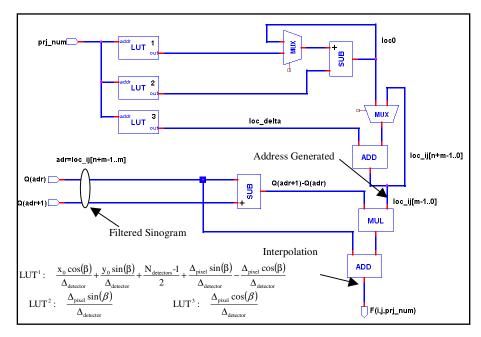

Figure 3.6 shows a more detailed hardware structure based on the data flow shown in Figure 3.3. This design uses three look up tables [3].

The reconstruction begins from the upper-most pixel furthest to the left, and continues in raster-scan order. For each pixel, once the address of the sinogram is generated, the corresponding two pieces of sinogram data will be read from memory for linear interpolation. We define the address generation and interpolation as one computation.

Figure 3.6: Hardware Structure

Table 3.1 gives the total available resources of two different Xilinx FPGA chips that were used to implement this design.

Table 3.1 WildStar and FireBird Specifications

|              | XCV1000, BG560 | XCV2000E, FG860 |

|--------------|----------------|-----------------|

|              | (WildStar)     | (FireBird)      |

| System Gates | 1,124,022      | 2,541,952       |

| CLB Array    | 64*96          | 80*120          |

| Logic Cells  | 27,648         | 43,200          |

| Maximum I/O  | 404            | 660             |

| Block RAM    | 32*4,096       | 160*4,096       |

Our design entry is a combination of user-specified and vendor-provided VHDL code. Implementation processing is automatically customized for the targeted device by the design tools. We used Synplicity design tools for VHDL synthesis. To take advantage of the inherent architectural features of the Xilinx FPGA architectures, such as Fast Carry Logic for arithmetic functions and on-chip RAM for dual-port and synchronous RAM, we also used Core Generator, a Xilinx tool. The block RAM component generated by Core Generator has higher priority than automated block RAM allocation. This means that if there are still unused block RAMs, the implementation process will use these for other non-Core Generator Modules when necessary. But if Core Generator Modules consume all the block RAMs, the implementation process will use other distributed memory or LUTs to implement other modules instead.