# NORTHEASTERN UNIVERSITY

# Graduate School of Engineering

| Thesis Title: Multimedia Macros for Portable Optimize | ed Programs      |   |

|-------------------------------------------------------|------------------|---|

| Author: Juan Carlos Rojas                             |                  |   |

| Department: Electrical and Computer Engineering       |                  |   |

| Approved for Thesis Requirement of the Doctor of Ph   | nilosophy Degree |   |

|                                                       |                  |   |

| Thesis Advisor                                        | Date             |   |

| Thesis Committee Member                               | Date             |   |

| Thesis Committee Member                               | Date             |   |

| Thesis Committee Member                               | Date             | - |

| Department Chair                                      |                  |   |

| Director of the Graduate School                       | <br>Date         |   |

# NORTHEASTERN UNIVERSITY

# Graduate School of Engineering

| Thesis Title: Multimedia Macros for Portable Op | ptimized Programs       |  |

|-------------------------------------------------|-------------------------|--|

| Author: Juan Carlos Rojas                       |                         |  |

| Department: Electrical and Computer Engineer    | ing                     |  |

| Approved for Thesis Requirement of the Doctor   | or of Philosophy Degree |  |

|                                                 |                         |  |

| Thesis Advisor                                  | <br>Date                |  |

| Thesis Committee Member                         | <br>Date                |  |

| Thesis Committee Member                         | <br>Date                |  |

| Thesis Committee Member                         | <br>Date                |  |

| Department Chair                                | <br>Date                |  |

|                                                 |                         |  |

| Director of the Graduate School                 | Date                    |  |

| Copy Deposited in Library:                      |                         |  |

| Reference Librarian                             | <br>Date                |  |

# MULTIMEDIA MACROS FOR PORTABLE OPTIMIZED PROGRAMS

A Thesis Presented

by

Juan Carlos Rojas

to

The Department of Electrical and Computer Engineering

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in the field of

Electrical Engineering

Northeastern University Boston, Massachusetts

August 2003

ABSTRACT

MULTIMEDIA MACROS FOR PORTABLE

**OPTIMIZED PROGRAMS**

by

Juan Carlos Rojas

Northeastern University, Boston

Thesis Advisor: Professor Miriam Leeser

Multimedia processor architectures offer a combination of long partitioned registers and

complex instructions that can speed up applications significantly when programmed manually.

Optimized programs for these architectures have been non-portable up to now, because of

differences in the instruction sets, register lengths, alignment requirements and programming

styles. This dissertation presents a method that overcomes all these obstacles by providing a

virtual instruction set common to a group of target architectures. This virtual instruction set is

implemented as a library of C pre-processor macros called MMM. The macros can emulate

long registers on architectures with short ones, and emulate complex instructions that are

missing in certain targets.

This research is the first to provide a general solution to the portability of optimized

multimedia programs. No other method to date allows an arbitrary program to take advantage

of the complex partitioned operations available in multimedia instruction sets, while remaining

portable.

MMM libraries were implemented for MMX & SSE, SSE2, AltiVec and TriMedia TM1300 multimedia architectures. Three examples from video compression were implemented in a portable way using MMM. The examples include IDCT, block distance for motion estimation, and block distance with interpolation. The portable examples were automatically translated into optimized code for each of the targets. Their performance is comparable, and in several cases better, than equivalent examples optimized by the processor vendors.

To Ericka, Laura and Sofia

# CONTENTS

| Contents                                                   | v    |

|------------------------------------------------------------|------|

| Illustrations                                              | vii  |

| Tables                                                     | viii |

| Chapter 1: Introduction                                    | 1    |

| 1.1 Optimization vs. Portabilty                            | 2    |

| 1.2 MMM                                                    | 2    |

| 1.3 Other Approaches                                       | 3    |

| 1.4 Contributions                                          | 4    |

| 1.5 Organization of this Dissertation                      |      |

| Chapter 2: Problem Description                             |      |

| 2.1 Background                                             | 6    |

| 2.2 Problem                                                | 11   |

| 2.3 Solution                                               | 14   |

| 2.4 Related Work                                           | 17   |

| 2.4.1 Parallelizing Compilers                              | 17   |

| 2.4.2 Data-Parallel Languages                              | 19   |

| 2.4.3 Optimized Libraries                                  | 22   |

| 2.4.4 Code Generation from Abstract Descriptions           | 24   |

| 2.4.5 Other Related Research                               | 26   |

| 2.5 Summary                                                |      |

| Chapter 3: Research                                        | 27   |

| 3.1 Objectives                                             |      |

| 3.1.1 Portability                                          | 27   |

| 3.1.2 Performance                                          | 28   |

| 3.2 Methodology                                            | 29   |

| 3.2.1 Target Architecture Selection                        |      |

| 3.2.2 Definition of a Common Virtual Instruction Set       |      |

| 3.2.3 Implementation of an MMM Library for each Target     | 35   |

| 3.2.4 Example Program Selection                            |      |

| 3.2.5 Analysis of Reference Implementations of Examples    |      |

| 3.2.6 Implementation of Portable Optimized Examples in MMM | 44   |

| 3.2.7 Performance Measurement                              |      |

| 3.3 Summary                                                |      |

| Chapter 4: Common Virtual Instruction Set                  | 47   |

| 4.1 Vector Declarations                                    | 48   |

| 4.2 Set Instructions                                       |      |

| 4.3 Load and Store Instructions                            |      |

| 4.4 Rearrangement Instructions                             |      |

| 4.5 Conversion Instructions                                |      |

| 4.6 Bit-wise Logic Instructions                            |      |

| 4.7 Shift Instructions                                     |      |

| 4.8 Floating-Point Arithmetic Instructions                 | 62   |

| 4.9 Integer Arithmetic Instructions                   | 63  |

|-------------------------------------------------------|-----|

| 4.10 Comparison Instructions                          | 70  |

| 4.11 Summary                                          | 71  |

| Chapter 5: Example Programs                           | 72  |

| 5.1 8x8 IDCT                                          | 72  |

| 5.1.1 Horizontal IDCT                                 | 73  |

| 5.1.2 Vertical IDCT                                   | 79  |

| 5.1.3 Target-Specific Optimizations                   | 83  |

| 5.2 16x16 L <sub>1</sub> -Distance                    |     |

| 5.2.1 Portable MMM Design                             | 84  |

| 5.2.2 Target-Specific Optimizations                   |     |

| 5.3 16x16 L <sub>1</sub> -Distance with Interpolation | 87  |

| 5.3.1 Portable MMM Design                             | 87  |

| 5.3.2 Target-Specific Optimizations                   | 90  |

| 5.4 Summary                                           | 90  |

| Chapter 6: Results                                    | 91  |

| 6.1 TriMedia TM1300                                   | 92  |

| 6.2 MMX + SSE                                         | 95  |

| 6.3 SSE2                                              | 95  |

| 6.4 AltiVec                                           |     |

| Chapter 7: Conclusions and Future Work                | 107 |

| 7.1 MMM Limitations                                   |     |

| 7.2 The Next Step: MMC                                |     |

| Appendix A: Virtual Instruction Set Definition        |     |

| A.1 Vector Declaration                                | 111 |

| A.2 Set Instructions                                  | 112 |

| A.3 Load and Store Instructions                       | 113 |

| A.4 Rearrangement Instructions                        | 115 |

| A.5 Conversion Instructions                           | 116 |

| A.6 Bit-wise Logic Instructions                       | 117 |

| A.7 Shift Instructions                                | 118 |

| A.8 Floating-Point Arithmetic Instructions            | 119 |

| A.9 Integer Arithmetic Instructions                   | 119 |

| A.10 Comparison Instructions                          | 122 |

| Appendix B: MMM Library Implementation                | 123 |

| B.1 TriMedia TM1300                                   |     |

| B.2 MMX + SSE                                         | 129 |

| B.3 SSE2                                              | 133 |

| B.4 AltiVec                                           | 136 |

| Appendix C: MMM Example Programs                      | 140 |

| C.1 8x8 IDCT                                          |     |

| C.2 16x16 L <sub>1</sub> -Distance                    |     |

| C.3 16x16 L <sub>1</sub> -Distance with Interpolation |     |

| Glossary                                              |     |

| Bibliography                                          | 152 |

# ILLUSTRATIONS

| Figure 2.1 Speedup of hand entimized multimedia bernels ever scalar versions | 10  |

|------------------------------------------------------------------------------|-----|

| Figure 2.1 Speedup of hand-optimized multimedia kernels over scalar versions |     |

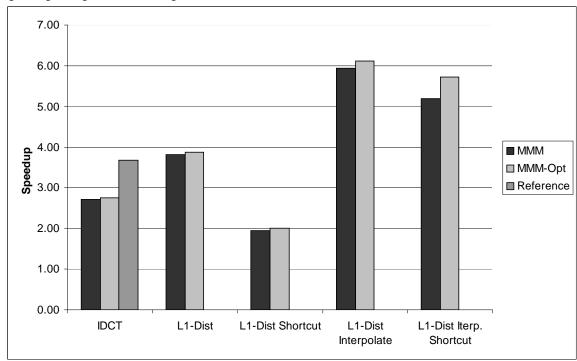

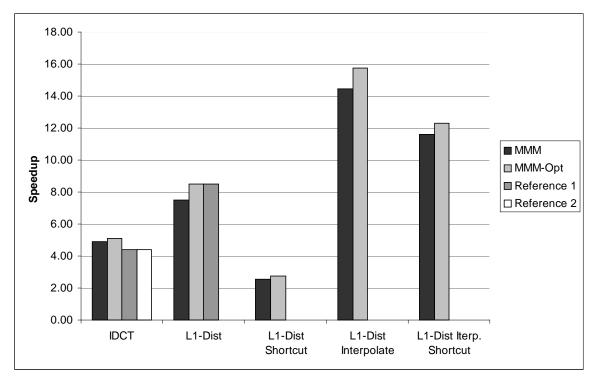

| Figure 6.1 Speedup of optimized examples on TriMedia TM1300                  | 93  |

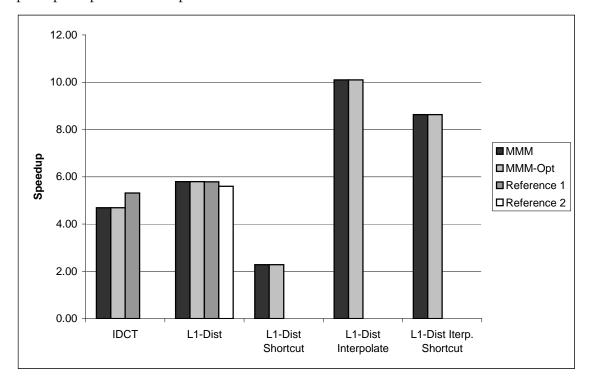

| Figure 6.2 Speedup of optimized examples on MMX + SSE                        | 96  |

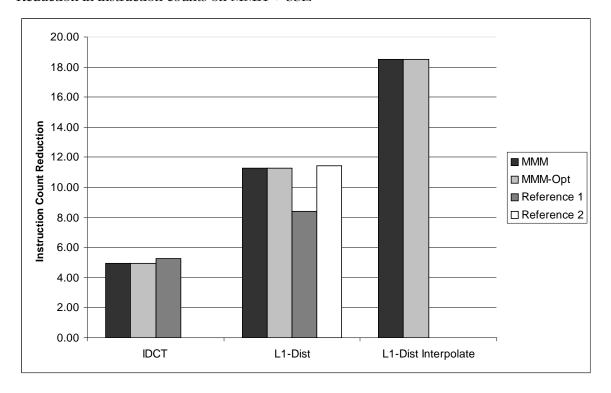

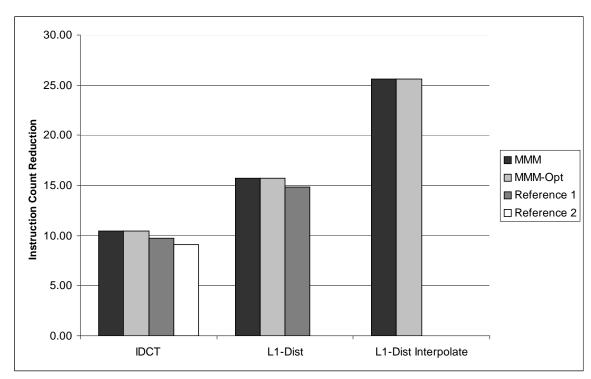

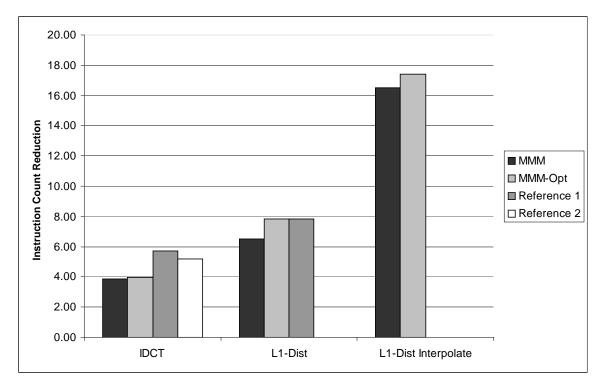

| Figure 6.3 Reduction in instruction counts on MMX + SSE                      |     |

| Figure 6.4 Speedup of optimized examples on SSE2                             | 100 |

| Figure 6.5 Reduction in instruction counts on SSE2                           | 101 |

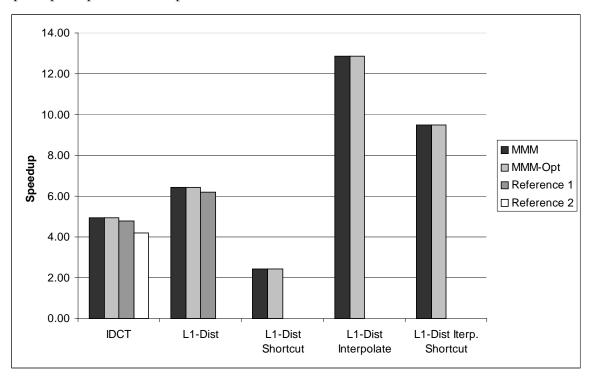

| Figure 6.6 Speedup of optimized examples on AltiVec                          | 103 |

| Figure 6.7 Reduction in instruction counts on AltiVec                        | 105 |

# TABLES

| Table 2.1 Popular processors that have multimedia instruction sets                     | 7   |

|----------------------------------------------------------------------------------------|-----|

| Table 2.2 Some complex parallel instructions supported by multimedia architectures     |     |

| Table 2.3 Published results for speedup                                                |     |

| Table 2.3 Different styles for declaration and operations on partitioned data          | 11  |

| Table 3.1 Characteristics of the instruction sets in the selected target architectures | 30  |

| Table 4.1 MMM vector declarations                                                      |     |

| Table 4.2 MMM set instructions                                                         | 52  |

| Table 4.3 Implementations of vector load macro on all targets                          | 52  |

| Table 4.4 MMM load and store instructions                                              | 55  |

| Table 4.5 MMM rearrangement instructions                                               | 57  |

| Table 4.6 MMM conversion instructions                                                  |     |

| Table 4.7 MMM bit-wise logic instructions                                              | 60  |

| Table 4.8 MMM shift instructions                                                       |     |

| Table 4.9 MMM floating-point arithmetic instructions                                   | 63  |

| Table 4.10 MMM integer arithmetic instructions                                         | 69  |

| Table 4.11 MMM comparison instructions                                                 | 70  |

| Table 6.1 Execution times in cycles on TriMedia TM1300                                 | 92  |

| Table 6.2 Speedup of optimized examples on TriMedia TM1300                             | 93  |

| Table 6.3 Instruction counts on TriMedia TM1300                                        | 94  |

| Table 6.4 Reduction in instruction counts on TriMedia TM1300                           | 94  |

| Table 6.5 Execution times in cycles on MMX + SSE                                       | 95  |

| Table 6.6 Speedup of optimized examples on MMX + SSE                                   | 95  |

| Table 6.7 Instruction counts on MMX + SSE                                              | 97  |

| Table 6.8 Reduction in instruction counts on MMX + SSE                                 | 97  |

| Table 6.9 Execution times in cycles on SSE2                                            | 99  |

| Table 6.10 Speedup of optimized examples on SSE2                                       | 99  |

| Table 6.11 Instruction counts on SSE2                                                  |     |

| Table 6.12 Reduction in instruction counts on SSE2                                     |     |

| Table 6.13 Execution times in clocks on AltiVec                                        |     |

| Table 6.14 Speedup of optimized examples on AltiVec                                    | 102 |

| Table 6.15 Instruction counts on AltiVec                                               |     |

| Table 6.16 Reduction in instruction counts on AltiVec                                  |     |

| Table A.1 MMM vector declaration macros                                                |     |

| Table A.2 MMM set instructions                                                         |     |

| Table A.3 MMM load and store instructions                                              |     |

| Table A.4 MMM rearrangement instructions                                               |     |

| Table A.5 MMM conversion instructions                                                  | 116 |

| Table A.6 MMM bit-wise logic instructions                                              |     |

| Table A.7 MMM shift instructions                                                       |     |

| Table A.8 MMM floating-point arithmetic instructions                                   |     |

| Table A.9 MMM integer arithmetic instructions                                          |     |

| Table A.10 MMM comparison instructions                                                 | 122 |

# Chapter 1

#### INTRODUCTION

Multimedia computing has been one of the greatest challenges in computer engineering for the last decade. Great efforts have been put into developing applications that process audio, video and graphics information. At the same time, computer designers have been challenged to come up with solutions capable of processing the enormous amounts of data required by multimedia applications. The solutions came in the form of multimedia processors, and multimedia extensions to general-purpose processors.

Nowadays, most commercial general-purpose processors support some form of multimedia extension. Some well-known examples are MMX extensions to Pentium processors, and AltiVec extensions to PowerPC. All multimedia architectures follow the same basic approach: they partition the registers into sections that represent multiple data elements, and operate on all the sections in parallel. In addition, they added complex instructions to speed-up specific tasks found in multimedia applications. For example, some architectures include an instruction to compute the sum of absolute differences of two vectors, which is useful in video compression.

# 1.1 Optimization vs. Portabilty

My experiments and other published results show that multimedia architectures can speed-up applications by factors of up to 15, but manual optimization is required in order to take full advantage of the complex instructions available. Manual optimization is very time consuming, and up to now has resulted in non-portable programs. This is in part because different multimedia architectures have different register lengths, different programming styles, different alignment requirements, and they support different partitioned instructions.

## **1.2 MMM**

I solved the problem by creating MMM: a library of target-independent C pre-processor macros that implements a common set of parallel operations available or efficiently emulated on a given set of target architectures. The contents of the library depend on the set of target architectures used, but the method can be applied to any group of target processors.

MMM provides a unique interface to architectures with different register lengths and instruction sets. Long data vectors are simulated by several small vectors, and operations of long vectors are emulated as a sequence of operations on short vectors. Similarly, vector operations that are missing on a given target are emulated using a sequence of simple vector operations, when it is efficient to do so. The same concept is used to resolve different alignment requirements. Some architectures require that vector loads and stores are done at aligned addresses. If an unaligned load is required, one must load two aligned vectors, and compose the desired result from them. All this can be encapsulated inside an MMM load macro, and thus provide with a general unaligned load virtual instruction.

Through emulation, MMM implements a large common virtual instruction set for several target architectures. By using MMM, it is possible to write multimedia applications that are portable among different multimedia processors, and take advantage of the complex partitioned operations available on them. I used it to write optimized versions of Inverse Discrete Cosine Transform of 8x8 blocks, and several variants of L<sub>1</sub>-Distance of 16x16 blocks.

MMM programs are portable among diverse multimedia architectures. Using MMM, I was able to generate optimized code for Pentium III with MMX and SSE extensions, Pentium 4 with SSE2 extensions, PowerPC G4 with AltiVec extensions, and Philips TriMedia multimedia processors, all from the same source program. The performance of my example programs is comparable, and in several cases exceeds that of hand-optimized versions of the same programs provided by the processor vendors.

# 1.3 Other Approaches

Parallelizing compilers can generate some multimedia instructions from scalar code, but not the most complex ones. The problem is that some these complex parallel instructions cannot be expressed compactly in C, only through a sequence of operations that is very hard for a compiler to recognize. One can also write parallel programs explicitly using a data-parallel language. But this still does not solve the problem of expressing complex parallel instructions. The other alternatives are to write applications based on optimized kernel libraries, or use automatic code generators from abstract descriptions. These are good solutions for certain kinds of applications, but not a general solution. MMM is a more flexible approach.

#### 1.4 Contributions

This research is the first to provide a general solution to the portability of optimized multimedia code. No other method to date allows an arbitrary program to take advantage of the complex partitioned operations available in multimedia instruction sets, while remaining portable. MMM can be used to write complex programs that are portable, yet perform comparably to hand-optimized versions for a single target. Parallelizing compilers only obtain comparable performance on simple programs. MMM is a flexible, general framework for writing multimedia programs; other optimized libraries are made up of kernels with limited applicability.

Most research on code generation for multimedia architectures uses simple, inherently parallel programs as examples. I used complex examples taken from real multimedia applications, and demonstrated that they can be written efficiently using MMM.

This research can generate optimized code for different families of multimedia architectures. Others have focused on a single kind of architecture: some for MMX-like architectures (SSE, SSE2, 3DNow!), some others for AltiVec, and some others for TriMedia. I was able to generate optimized code for very different kinds of multimedia architectures: MMX, SSE, SSE2, AltiVec and TriMedia.

# 1.5 Organization of this Dissertation

This dissertation is organized into six chapters besides this introduction. Chapter 2 describes in more detail the problem addressed by this research, presents the solution in depth, and relates it to other research approaches. Chapter 3 covers the methodology: defines the research objectives, and explains the steps followed to validate that they have been met. Then Chapter 4 discusses the design of a virtual instruction set. The example programs are covered in Chapter 5, and Chapter 6 presents the performance measurement results. Chapter 7 has conclusions, and advances on future research work.

In addition, there are three appendices. Appendix A shows the complete definition of the virtual instruction set. Appendix B has the actual implementation of the MMM library for the different targets, and Appendix C is the source code of the portable examples written in MMM.

#### PROBLEM DESCRIPTION

This chapter discusses in depth the problem addressed by this dissertation, the solution presented, and related research. The first section introduces characteristics of multimedia architectures and how they are programmed. Section 2.2 describes the factors that make the portability of optimized programs a problem. Next, Section 2.3 explains how MMM can solve all these portability problems. Section 2.5 compares MMM to other approaches to the same problem.

# 2.1 Background

Multimedia applications are computationally very intensive for general-purpose processors, as they have to process enormous amounts of data. Processor designers have responded by adding multimedia instruction sets with partitioned registers and parallel SIMD instructions, including some complex instructions specifically tailored for multimedia applications. Table 2.1 shows a list of popular architectures that have multimedia instruction sets. They come in the form of multimedia extensions to general-purpose processors, or as special-purpose multimedia processors. There is a large variation in the length of the multimedia registers in these processors, from 32 bits to 128 bits.

Table 2.1 Popular processors that have multimedia instruction sets

| Instruction Set             | Architecture Type                                                  | Register Length                                       | Reference |

|-----------------------------|--------------------------------------------------------------------|-------------------------------------------------------|-----------|

| SSE2                        | Multimedia extensions to Intel<br>Pentium 4 processors             | 128 bits                                              | [37]      |

| MMX + SSE                   | Multimedia extensions to Intel<br>Pentium III and later processors | 64 bits for integer<br>128 bits for<br>floating point | [37]      |

| AltiVec                     | Multimedia extensions to Motorola<br>PowerPC G4 processors         | 128 bits                                              | [36]      |

| Enhanced 3DNow!             | Multimedia extensions to AMD<br>Athlon processors                  | 64 bits                                               | [38]      |

| VIS                         | Multimedia extensions to SUN<br>UltraSparc processors              | 64 bits                                               | [39]      |

| Phillips TriMedia<br>TM1300 | Multimedia processor                                               | 32 bits                                               | [35]      |

| Equator MAP-CA              | Multimedia processor                                               | 64 and 128 bits                                       | [40]      |

Multimedia data elements can often be represented by 8-bit or 16-bit integers. For example, image pixels are represented by 8 bits for each color component. It is possible to hold 16 pixels in a single 128-bit register, and operate on all of them in parallel. Multimedia architectures have been designed specifically to take advantage of this parallelism, by using long registers and partitioned instructions. While longer registers have a greater potential for speedup, it is not always possible to take full advantage of them; it depends on the amount of parallelism available in the algorithm.

Multimedia processors vary in the instructions they implement. All of the processors in Table 2.1 support basic integer arithmetic and logical instructions on registers partitioned into 8, 16 and 32-bit sections. Many support complex instructions like sad (sum of absolute differences), and multiply-add-pairs (parallel multiply and add adjacent pairs of products). Some support parallel floating-point operations too. Table 2.2 shows some of the complex parallel operations present in multimedia instruction sets.

Table 2.2

Some complex parallel instructions supported by multimedia architectures

| come complex parallel histractions supported by maintinedia are intectures |      |              |         |                    |     |        |        |

|----------------------------------------------------------------------------|------|--------------|---------|--------------------|-----|--------|--------|

| Instruction                                                                | SSE2 | MMX<br>+ SSE | AltiVec | Enhanced<br>3DNow! | VIS | TM1300 | MAP-CA |

| sad<br>(sum of absolute differences)<br>of 8-bit integers                  | V    | V            |         | V                  | V   | V      | V      |

| multiply-add-pairs of 16-bit integers                                      | √    | √            | √       | V                  |     | V      |        |

| multiply-high of 16-bit integers                                           | √    | √            | √       | V                  |     |        | V      |

| Average of 8-bit integers                                                  | √    | √            | √       | V                  |     | V      | V      |

| maximum and minimum of 8-bit integers                                      | V    | √            | √       | V                  |     | V      | V      |

Optimized multimedia programs take advantage of the complex partitioned operations available on the target architecture, to obtain significant speedups with respect to scalar implementations. The speedup that can be obtained by using multimedia instruction sets varies, depending on the architecture and the application. Published results range from no speedup, up to factors of 12 for manually optimized multimedia and signal processing kernels. Selected published results are listed in Table 2.3. Refer to the Glossary at the end of this dissertation for definitions of the acronyms in this table.

Table 2.3 Published results for speedup obtained by hand-optimization using multimedia instruction sets

| Benchmark                            | Target  | Speedup     | Reference |

|--------------------------------------|---------|-------------|-----------|

| FIR                                  | VIS     | 3.43        | [1]       |

| MPEG encoder                         | VIS     | 3.1         | [2]       |

| MPEG2 decoder                        | MMX     | 1.4 – 1.5   | [3]       |

| IDCT                                 | MMX     | 3.25 - 4.37 | [3]       |

| H.263 encoder                        | MMX     | 1.67        | [4]       |

| FFT                                  | MMX     | 1.98        | [5]       |

| Motion Estimation with Interpolation | MMX     | 3.1         | [6]       |

| IDCT                                 | AltiVec | 11.7        | [7]       |

| FIR                                  | AltiVec | 3.1         | [8]       |

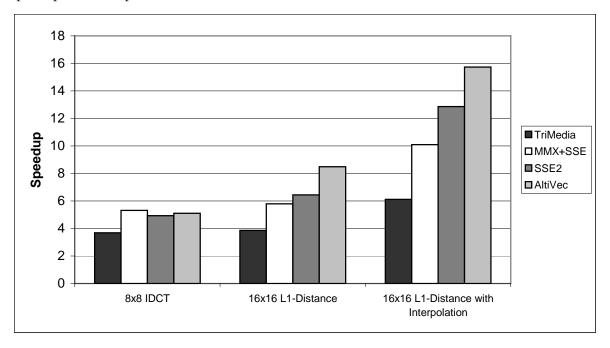

My own research shows that speedups of up to a factor of 15 can be obtained through manual optimization on different multimedia architectures. Figure 2.1 compares the speedup obtained by using complex partitioned instructions for several multimedia kernels on different architectures. More details about these measurements are available in Chapter 6.

Figure 2.1 Speedup of hand-optimized multimedia kernels over scalar versions.

Optimized multimedia programs are usually written in extended versions of C. Partitioned instructions are expressed by macros or functions called intrinsics. The alternatives to writing optimized programs in C with intrinsics are to write them in assembly, or to use libraries, a vectorizing compiler, or an automatic code generator. These approaches are discussed in Section 2.4.

Development environments for different multimedia architectures have different styles to define parallel data and operations. Table 2.3 shows several styles for a simple vector declaration and parallel addition. AltiVec uses the *vector* type qualifier to define vectors of basic types; operations infer the partition size from the type. TriMedia uses integers to represent vectors, and the partition sizes are specified by the operations. Intel supports both models: it has a set of C intrinsics that specify partition sizes, and also overloaded C++ operators for vector classes that infer the partition size from the argument type.

Table 2.3

Different styles for declaration and operations on partitioned data

| Architecture             | Example                 |                                                                      |

|--------------------------|-------------------------|----------------------------------------------------------------------|

| TriMedia                 | int A, B, C;            | /*Each variable represents a vector of 2 16-bit values*/             |

|                          | A = DSPIDUALADD(B, C);  | /*Parallel add*/                                                     |

| AltiVec                  | vector short A, B, C;   | /*Each variable represents a vector of 8 16-bit values*/             |

|                          | A = vec_add(B, C);      | /*Parallel add*/                                                     |

| Intel C intrinsics       | m64 A, B, C;            | <pre>/*Each variable represents a  vector of 4 16-bit values*/</pre> |

| munisies                 | A = _mm_add_pi16(B, C); | /*Parallel add */                                                    |

| Intel C++ vector classes | I16vec8 A, B, C;        | <pre>/*Each variable represents a  vector of 8 16-bit values*/</pre> |

| , cetter emisses         | A = B + C;              | /*Parallel add */                                                    |

## 2.2 Problem

Multimedia programs written in C can be optimized to take advantage of the complex partitioned operations available in multimedia instruction sets by using intrinsics. These optimized programs are not portable to other architectures, even if the instruction sets are similar. Differences in register lengths, instructions supported, data alignment requirements and programming styles are obstacles to portability. Portable programs are desirable, but up to now there has been no way to make complex portable programs run as fast as hand-optimized ones.

The length of the registers on current multimedia architectures can vary from 32 to 128 bits, as shown in Table 2.1. For highly parallel algorithms and large input blocks, optimized programs iterate over the input data in sections the size of the registers. The number of iterations is inversely proportional to the register length.

The available partitioned instructions vary from architecture to architecture. For example, the sad instruction for 8-bit partitions is available on many processors, but not on AltiVec. The multiply-high instruction is available on TriMedia for 8-bit partitions, but not for 16-bit partitions. SSE and SSE2 support multiply-high on 16 and 32-bit partitions, and one operand can be a memory address. AltiVec has a variant of this instruction for 16-bit partitions only, where it adds the 17 most significant bits of the product, adds it to the corresponding partition of a third input vector, and returns the saturated 16-bit result.

Some processors require aligned vector loads and stores. For example, TriMedia can only read 32-bit words from addresses that are in a 32-bit boundary (the last 5 bits of the address are zero). Similarly, AltiVec can only read and write vectors on addresses that are 128-bit aligned. If one needs to load a vector from an unaligned address, one needs to load two vectors and extract the desired data from them. Intel SSE can read from unaligned addresses without any restriction. SSE2 has, in addition, fast load/store instructions for 128-bit aligned addresses.

There are obvious advantages from optimized programs. They can boost the performance of high-end processors, or perform equivalent tasks on lower-cost processors. But there are also benefits to portability. Optimizing programs is an expensive, time-consuming job, which has to be repeated for every target architecture. Having multiple versions of a program is hard to maintain and is prone to errors.

Scalar C programs are portable, but not optimized. Even parallelizing compilers cannot fully take advantage of the complex partitioned operations available in multimedia instruction sets. Compilers can generate basic parallel operations, like additions of floating-point multiplications on partitioned registers, but not complex ones. The problem is that C lacks syntax to explicitly express many complex operations available in DSP and multimedia instruction sets, like multiply-high, sad, or saturating arithmetic operations. Such instructions can only be expressed through a complex sequence of operations that is very hard for a compiler to recognize. Consider the case of the sum of absolute differences (sad) of two vectors of 16 8-bit integers. To express this operation in C would require a loop, in which the absolute value of the difference of the elements is summed:

```

sad = 0;

for (i=0; i<16; i++)

{

diff = a[i] - b[i];

sad += diff > 0 ? diff : -diff;

}

```

Several other representations are also possible for this operation. Complex operations like *sad* are awkward to write in C, and hard for compilers to recognize.

The only way to exploit the full potential of multimedia processors is to program in C with intrinsics or in assembly. Processor vendors provide compilers that support intrinsics for their own processors. Each architecture follows its own style, as was seen in the examples in Table 2.3.

2.3 Solution

Multimedia architectures differ in certain aspects, but are also similar in many ways. They are

all programmable in C with intrinsics, the register lengths are all multiples of basic types, and

similar partitioned instructions exist on them. Even if the instruction sets are not identical, it is

often possible to emulate the missing instructions efficiently with a sequence of the available

instructions. Similarly, parallel operations on long registers can be emulated with a sequence

of operations on short registers.

My solution is to create a library of target-independent C pre-processor macros called MMM –

for Multimedia Macros - that implements a common set of parallel operations available or

efficiently emulated on a given set of target architectures. The programs use MMM macros as

virtual instructions, which get translated by the libraries to C code with intrinsics for each

target architecture. The C output is compiled to a program executable by the regular C

compiler provided by each processor vendor. By using MMM, it is possible to write

multimedia applications that are portable among different multimedia processors, and take

advantage of the complex partitioned operations available on them.

MMM makes it possible to create portable programs for target architectures that have different

register lengths. A long vector can be represented by several short vectors, and operations on

long vectors can be emulated by repeated operations on short vectors. For example, if you

wanted to load and add two arrays of 8 16-byte integers, you would write it in MMM as:

DECLARE\_I16x8(A);

DECLARE\_I16x8(B);

DECLARE\_I16x8(C);

14

```

LOAD_A_I16x8(A, pSrcA);

LOAD_A_I16x8(B, pSrcB);

ADD_I16x8(C, A, B);

```

In this example, A, B and C represent 128-bit vectors, and the loads are from aligned addreses. The mapping of these macros to an architecture with 128-bit registers is straightforward. For example, the implementation of these macros for SSE2 is:

```

#define DECLARE_I16x8(var) \

__ml28i var;

#define LOAD_A_I16x8(var, ptr) \

var = _mm_load_si128((__ml28i *) (ptr));

#define ADD_I16x8(dst, src1, src2) \

dst = _mm_add_epi16(src1, src2);

```

On architectures with registers smaller than 128 bits, these vectors are represented by several variables. TriMedia has 32-bit registers, so it needs to use four variables to represent each vector, and replicate the operations four times:

```

#define DECLARE_I16x8(var) \

unsigned int var##_0; \

unsigned int var##_1; \

unsigned int var##_2; \

unsigned int var##_3;

#define LOAD_A_I16x8(var, ptr) \

var##_0 = *((int *) (ptr)); \

var##_1 = *(((int *) (ptr))+1); \

var##_2 = *(((int *) (ptr))+2); \

var##_3 = *(((int *) (ptr))+3);

#define ADD_I16x8(dst, src1, src2) \

dst##_0 = DSPIDUALADD(src1##_0, src2##_0); \

dst##_1 = DSPIDUALADD(src1##_1, src2##_1); \

dst##_2 = DSPIDUALADD(src1##_2, src2##_2); \

dst##_3 = DSPIDUALADD(src1##_3, src2##_3);

```

The pre-processor construct ## represents concatenation, so four different variable names are generated from the macros. For example, DECLARE\_I16x8(A) gets resolved as:

```

unsigned int A_0; unsigned int A_1;

```

```

unsigned int A_2; unsigned int A_3;

```

This technique uses several local variables to represent vectors. This is not a problem for register scheduling, because the variables are independent of each other and the compiler can schedule several of them into the same registers. The replication of the operations is equivalent to loop unrolling, a technique that many hand-optimized programs use anyway.

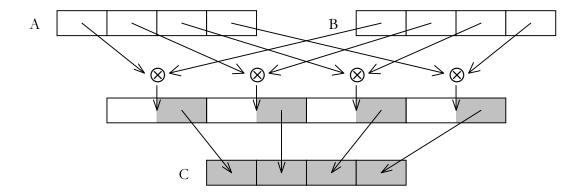

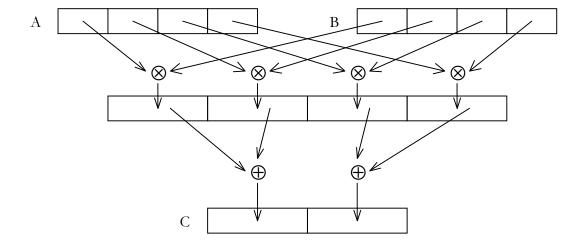

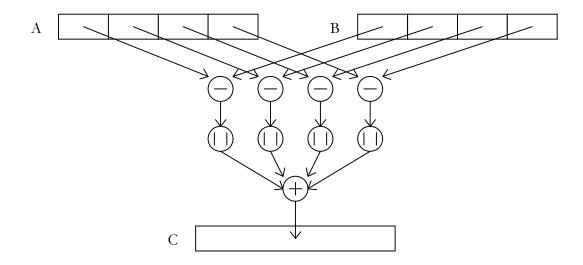

Some processors don't support certain instructions available in other ones. However, it is often possible to emulate these instructions efficiently with a sequence of operations. The idea is to use emulation only to simulate an instruction available in one of the target processors, in order to maintain the libraries at the instruction level and maximize reusability. For example, a sad instruction is not available in AltiVec, but can be emulated by using parallel maximum, minimum and subtract, followed by a sum of vector elements. Below is a simplified implementation of sad on AltiVec. Two operations are required to sum all 16 elements of the vector:

```

#define SAD_U8x16(dst, src1, src2) \

dst = vec_sums( vec_sum4s( vec_sub( \

vec max(src1, src2), vec min(src1, src2))));

```

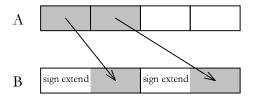

Differences in alignment requirements can also be overcome by using MMM. Separate macros for aligned and unaligned loads and stores allow the programmer to avoid re-alignment overhead when it is not required. Unaligned loads can be implemented with a sequence of operations that extract the unaligned data from two aligned vectors. For example, TriMedia requires word loads to be from 32-bit aligned addresses. If an address is unaligned, the load behaves as if the lowest 5 bits of the address were zero. Unaligned loads can be implemented by loading two words beginning at the previous 32-bit boundary, and extracting the desired word with *shifts* and *ors*:

MMM can overcome the differences in programming styles for different architectures by providing a common set of macros to define and manipulate partitioned data. The examples above show how vectors can be declared and loaded in a machine-independent fashion. Other style-dependent manipulations, like setting vectors constants, or allocating aligned memory, can also be handled this way.

This research is focused on the problem of taking advantage of the complex parallel operations in multimedia instruction sets. There are other factors that affect the performance of a program, like the size of the caches, speed of the memory relative the CPU, instruction pipeline structure, operating system overhead, and compiler quality. This research does not attempt to address them. Sub-section 2.4.4 discusses complementary approaches that can deal with these issues.

## 2.4 Related Work

Researchers have approached the problem of portability of optimized code from four different angles: parallelizing compilers, data-parallel languages, optimized libraries, and automatic generation of optimized code from abstract descriptions. The next sub-sections analyze each of these approaches and describe the state of current research in these fields.

## 2.4.1 Parallelizing Compilers

A lot of research has been focused on generating partitioned instructions from scalar loops.

There are several commercial and experimental compilers that can parallelize code to some

degree. Highly-parallel programs, like vector and matrix multiplications, dot products and linear equation solvers, can be efficiently parallelized by compilers. More complex applications like IDCT or L<sub>1</sub>-Distance of blocks cannot. Compilers achieve only modest speedups on these types of kernels, if any.

A vectorizing compiler for MMX by Sreraman and Govindarajan [9] reports to have vectorized an L<sub>1</sub>-Distance loop, but as a sequence of simple parallel operations, and not using the *sad* instruction available in MMX+SSE.

Lorenz, Wehmeyer and Dräger [10] report success in vectorizing dot-product loops, but not convolution or FIR kernels on their compiler targeted at the M3 DSP processor. Larsen and Amarasinghe developed a vectorizing compiler for AltiVec [11]. Their speedup results are good for inherently-parallel programs like color conversion, but a modest 1.24 to 1.57 on FIR, IIR, and SPECfp kernels.

Leupers [12] developed a parallelizing compiler for TriMedia and TI C62xx processors. This compiler is able to recognize sum of products patterns, and thus is able to parallelize FIR filters for TriMedia. It can get 1.2 to 1.3 speedups on IIR and convolution for C62xx, but no speedup on these kernels for TriMedia.

The commercially available Intel C/C++ compiler reports good speedup results for dot products, vector-matrix and scalar-matrix products, LU factorization, and linear equation solving for SSE and SSE2 [13][14]. The speedups for SpecCPU benchmarks ranges from 1.03 to 1.23. My own experiments with version 7.0 of this compiler show that it cannot parallelize IDCT or L<sub>1</sub>-Distance kernels.

VectorC by Codeplay [15] is a vectorizing compiler aimed at games programming for MMX, SSE, SSE2 and 3DNow! It reports speedups from 1.5 to 2.9 on vector rotations, normalizations and projections. No results are reported for more complex examples.

Other experimental vectorizing compilers for VIS [16][17] only report successful vectorization of simple, single assignment loops. There are other commercial vectorizing compilers for AltiVec, by Green Hills Software and by Veridian Systems, and by The Portland Group for MMX, SSE, SSE2 and 3DNow!, but no speedup results are published.

Vectorizing compilers are an active area of research, and will undoubtedly improve in the future. They are a good solution for inherently parallel algorithms, like those in linear algebra, and to achieve modest speedups on existing scalar code. But vectorizing compilers are restricted by the lack of syntax in the C language to express complex operations available in multimedia instruction sets. In general, scalar C programs cannot achieve speeds comparable to hand-optimized versions.

#### 2.4.2 Data-Parallel Languages

Data-parallel languages allow definition of parallel data types of different shapes; operations on parallel variables are defined to be parallel operations on each of the elements. This maps well to SIMD architectures of different sorts, from multimedia processors to massively parallel computers. In addition to strictly parallel operations, data-parallel languages support broadcast and reduction operations between scalar and parallel variables.

A number of data-parallel languages have been defined for different kinds of computers. Any of these languages can express basic parallel arithmetic and logic operations, but cannot explicitly express complex operations like multiply-high or sad.

Fortran 90 can define array types and operate natively on them [18]. C\* supports parallel types of arbitrary shapes [19]. In both of these languages, parallel operations are limited to basic arithmetic and logic, plus minimum and maximum.

Vector Pascal [20] and SWARC [21][22] were designed specifically for multimedia instruction sets. They add syntax to express some more of the partitioned operations available in these architectures. SWARC supports parallel average, as well as saturation arithmetic to handle overflows. Vector Pascal supports saturating adds and subtracts, and allows user-defined unary functions to operate on vector variables. Although SWARC and Vector Pascal are richer than other data-parallel languages, they still cannot express many complex parallel operations like multiply-high or sad.

Some languages have been designed to express some of the complex operations typically available in DSP processors. For example, ISO Embedded C [23] provides native types for fixed-point variables, with qualifiers to specify either saturation or modulo arithmetic handling of overflow. It also defines native functions for absolute-value, round and count-bits. Using fixed-point types one can express a multiply-high operation, and can write a sad operation more concisely than in standard C, by using the absolute-value operator. Embedded C is a scalar language, so SIMD operations on vectors can only be expressed through a loop.

MMM is a macro library, but in a sense it is a data-parallel language. It can express vectors of data and parallel operations on them. It is different from others languages in that can express all kinds of complex parallel operations, and that it uses C pre-processor macros instead of language extensions. Using C pre-processor macros gives MMM an enormous flexibility to

expand as needed, and thus is useful in experimentation. The translation of MMM programs into C with target-specific intrinsics is very simple, and doesn't require a compiler.

The concept of C pre-processor macros as a portable language has been used before. Franchetti and Püschel [24] used macros to represent parallel loads/stores, parallel floating-point arithmetic operators, and permutations. MMM extends this idea to more complex operations, introduces the concept of emulation of instructions, and emulation of longer register lengths.

Partitioned data and operations can also be expressed with C++ classes and overloaded operators. This is the case of Intel's C++ SIMD Class Libraries [26]. C++ classes are defined for specific combinations of vector lengths and data types, and operators are overloaded to work on these types. For example, the F32vec4 class represents vectors of 4 32-bit floating-point elements. Overloaded operators exist for loads, stores, standard logic, arithmetic and shift operations, saturating-add and subtract, sum-vector-elements, maximum, minimum, average, parallel comparisons, data packing, conversions between floating-point and integer, multiply-high, multiply-add, square-root, and complex-reciprocal.

The classes and operations implemented by this library match part of the Intel MMX, SSE and SSE2 instruction sets. There are still some instructions in these architectures that are not implemented as overloaded operators, like sad, multiply-add-pairs, and permutations. Operators are only implemented for the classes that there is hardware support for; there is no emulation. For example, parallel multiplication is available for floats and for 16-bit integers, but not for 8 or 32-bit integers. Also, 128-bit vector classes and operators are only

implemented for SSE2, and not for MMX and SSE, so a program written with 128-bit classes does not run on a processor that does not have SSE2.

MMM and Intel C++ SIMD classes share the same philosophy: they implement a common interface for the instruction sets of different architectures; both implement only vector lengths and element types that are supported by hardware, not arbitrary lengths. The difference is that MMM emulates longer vector lengths on architectures with short registers, and complex operations on architectures that don't have them, when it is efficient to do so. A program written with 128-bit vectors using MMM can run on processors with 64 or 32-bit SIMD registers. One advantage of C++ classes over MMM is that it overloads operators for different vector lengths and types, which makes the syntax more elegant. MMM cannot overload, so a different macro must be used for each vector length and type. This is acceptable for this research, as it is just a matter of style. A C language extension for multimedia, with overloaded operations is proposed as future work in Chapter 7.

## 2.4.3 Optimized Libraries

An alternative way to write portable optimized programs is to base the application on libraries of kernels that have been hand-optimized for the different targets. The problem of this approach is that developing and maintaining a large number of libraries for a large number of targets is very laborious and expensive. Also, these libraries are inflexible; there is no room for customization.

There are some examples of libraries optimized for multiple targets, for specific applications. The most notorious is BLAS [27]. BLAS is a set of basic floating-point vector-vector, vector-matrix and matrix-matrix operations, which serves as a base for various linear algebra

packages, like LAPACK and LINPACK. BLAS has been optimized for virtually every processor by the vendors or users. Due to the parallel nature of the operations in BLAS, very efficient implementations can be achieved by using parallel operations in multimedia instruction sets. This library is useful for scientific computation, and no so much for multimedia applications.

More applicable for multimedia are Intel's Integrated Performance Primitives [28]. This library includes kernels for signal, image, speech, graphics and audio processing, and operates on vectors or matrices of integer or floating-point data. Optimized versions of these libraries are available for all current Intel architectures, including MMX, SSE, SSE2 and XScale. Naturally, this library is only available for Intel processors. Some other vendors have their own libraries of signal processing kernels.

An effort to consolidate signal-processing libraries to a unique API is VSIPL [29]. VSIPL is a standard for a very complete library of signal and image processing kernels, operating on integer and floating point types of various precisions. This library supports signal processing operations, like FFT, FIR and IIR filters, convolution, correlation, as well as arithmetic, logic and linear algebra on one, two and three-dimensional arrays. An interesting concept in VSIPL is the portable precision types, where the minimum precision required is specified. This allows an implementation to use a more precise type when it is more efficient. Implementations of VSIPL are done by different vendors, conforming to the standard API. Currently, the basic VSIPL profile has been implemented for SSE and AltiVec multimedia architectures.

MMM is a library, but at the instruction level, rather than at the kernel level. MMM operations are much more reusable than the libraries above. Kernel libraries like BLAS and VSIPL could actually be built based on MMM macros.

Another low-level vector library is CVL [30]. It provides a set of parallel arithmetic, logic and comparison operations, reductions and permutations for arbitrary length vectors. CVL serves as a machine-independent interface for higher-level data parallel languages like NESL. CVL is intended for scientific applications on massively parallel architectures, and has been optimized for CM-2, CM-5 and Cray Y-MP computers. CVL could be implemented on uniprocessor multimedia architectures, but it would suffer from the high overhead of a function call per vector operation.

## 2.4.4 Code Generation from Abstract Descriptions

Optimized code can sometimes be generated from abstract descriptions of an algorithm. Franchetti and Püschel explored this approach for matrix transformations in their SPIRAL project [24][25]. They generate multiple implementations of a given matrix transformation iteratively, searching for the best run-time performance. Their system decomposes the matrix into operators that are vectorizable, and generates the appropriate partitioned instructions. Their output is C code with macros that represent parallel loads/stores, parallel floating-point arithmetic, and permutations. The macros can be resolved to intrinsics for different architectures. They have currently implemented the macros for SSE and SSE2.

A similar method is used by FFTW [31][32] for the generation of FFT and similar transforms. The transforms are decomposed into "codelets" of different sizes according to a plan. The execution time of multiple plans is compared in search for the optimal one. Distributed with

the system comes a library of codelets, which were either hand-coded, or automatically generated a priori. The most recent version of FFTW can take advantage of SIMD instructions in SSE, SSE2, 3DNow! and AltiVec. It does so by using generic parallel instructions in SIMD versions of the codelets. The generic instructions are translated to specific architecture instructions by the code generator, according to a description file. FFTW uses parallel *load*, *store*, *add*, *subtract*, *multiply-add*, *mutiply-subtract*, *unpack*, and *permute* on floating-point elements.

Another self-optimization project is ATLAS [33]. It generates adapted implementations of the BLAS library of linear-algebra kernels, and applies dynamic programming to search for the plan with optimal execution time. The code generator can vary several parameters, like the minimum block size that fits in registers, loop unrolling factor, support for multiply-add instructions, and fetch patterns. ATLAS supports SIMD instructions, based on hand-coded kernel libraries provided by the user community.

Feedback-based automatic code generators like SPIRAL, FFTW and ATLAS can optimize for many aspects of a computer's architecture, like the size of the caches, number and size of registers, and support of certain instructions. MMM can complement this approach by providing a common interface to the instruction sets of different architectures. As a matter of fact, SPIRAL uses C pre-processor macros, much like MMM, to represent parallel operations in different architectures. SPIRAL and FFTW only use a small subset of multimedia instruction sets. MMM implements a larger common set of instructions, because it emulates complex instructions on architectures that don't have them. As a result, MMM provides a much richer set of machine-independent instructions that a code generator could use.

#### 2.4.5 Other Related Research

Some researchers have experimented with emulation of parallel operations on architectures that do not have explicit support for it, or to further subdivide existing partitions into smaller ones. Fisher and Dietz [21] describe how it is possible to execute parallel additions and subtractions without risk of carryover, by separating the elements with spacer bits. Zucker and Lee implemented partitioned addition, subtraction and multiplication by a scalar using floating-point instructions [34]. These techniques can easily be implemented within MMM macros.

## 2.5 Summary

Multimedia architectures can have different register lengths, alignment requirements, programming styles, and support different partitioned instructions. All these are obstacles to portability, but can be overcome by using MMM: a set of target-independent C pre-processor macros that provide an interface to the different target architectures. MMM emulates long vectors on architectures with short registers, and emulates complex instructions that are missing on some processors. MMM programs can be portable and optimized at the same time.

Other approaches are parallelizing compilers, data-parallel languages, optimized libraries, and automatic code generation from abstract descriptions. None of these methods provide the same level of performance and flexibility as MMM.

The next chapter describes the objectives and methodology used to validate MMM as a solution to the problem of portability of optimized code.

#### RESEARCH

This chapter describes the objectives and methodology followed by this research. Section 3.1 defines in detail the objectives that are addressed by MMM: portability and performance. Section 3.2 goes through all the steps that were followed in order to validate the objectives stated.

# 3.1 Objectives

The goal of this research is to validate MMM as a solution that allows multimedia programs to be portable and optimized at the same time. There are two major parts to this claim: that MMM programs are portable among diverse multimedia architectures, and that they have good performance on all the targets. The next two sub-sections elaborate more on these two objectives. Ease of programming is not an objective of this research, but will be addressed as future work in Chapter 7.

## 3.1.1 Portability

By portable I define a program with a single source, without machine-specific sections, that can be compiled for different targets and produce the desired results. The type of portability that MMM accomplishes in not unlimited, an MMM program will not necessarily be portable to all current and future multimedia architectures, while remaining optimized. But MMM should provide portability among several diverse architectures that would otherwise be incompatible.

I say desired results, and not identical results, because it may be possible to approximate an operation in a way that is not bit-exact, but close enough for practical purposes. For example, one implementation may use more precision in the multiplications than required. This is fine as long as there is a clear criteria defining what the desired results are.

The only machine-specific section that is allowed in portable MMM programs is the inclusion of the MMM header file for the current target. The header files for each target are conditionally included based on an environment definition:

```

#ifdef SSE2

#include "mmm_sse2.h"

#endif

#ifdef SSE

#include "mmm_sse.h"

#endif

#ifdef TRIMEDIA

#include "mmm_tm.h"

#endif

#ifdef ALTIVEC

#include "mmm_altivec.h"

#endif

```

## 3.1.2 Performance

In the context of this research, an optimized program is one that makes efficient use of the target's instruction set in order to reduce the number of instructions necessary to perform the task. Although the ultimate goal of optimization is to reduce the execution time, there are factors that affect it, like the memory structure and instruction pipeline interactions, which are beyond the scope of MMM. I use both instruction counts and execution speed as measures of performance, and attempt to minimize the effects of the memory structure on my experiments.

The performance of MMM optimized programs should be better than equivalent scalar programs, even when compiled with a parallelizing compiler. It is not expected that MMM programs out-perform hand-optimized programs for a single target, but they should come close. An objective of this research is to determine how much performance is lost in order to obtain portability.

## 3.2 Methodology

The rest of this chapter outlines a sequence of steps that I followed in order to validate that MMM meets the objectives stated above. The steps include selecting a diverse group of target architectures, defining and implementing a common virtual instruction set, selecting and implementing several example programs and comparing their performance.

## 3.2.1 Target Architecture Selection

I selected four different target architectures with multimedia instruction sets. They are: the TriMedia TM1300 media-processor [35], AltiVec extensions to the PowerPC G4 processor [36], SSE2 extensions to the Pentium 4 [37], and MMX and SSE extensions to the Pentium III combined [37]. SSE is complementary to MMX, and MMX is always supported whenever SSE is, so they can be considered a single architecture. MMX and SSE are also available on Pentium 4 processors, but the SSE2 instruction set largely supersedes the previous ones, so I consider them different architectures. These architectures are very diverse, and thus present a good challenge to portability. Table 3.1 shows some characteristics of their instruction sets. They differ in their register lengths, partition sizes and types that they support, as well as in the instructions available for each partition type. The next four sub-sections discuss the each of these instruction sets in more depth.

Table 3.1 Characteristics of the instruction sets in the selected target architectures

| Architecture                   | TM1300          | MMX + SSE           | SSE2                | AltiVec         |

|--------------------------------|-----------------|---------------------|---------------------|-----------------|

| Register length                | 32 bits         | 64 bits             | 128 bits            | 128 bits        |

| Integer partition types        | 8, 16 & 32 bits | 8, 16, 32 & 64 bits | 8, 16, 32 & 64 bits | 8, 16 & 32 bits |

| Floating point partition types | 32 bits         | 32 bits             | 32 & 64 bits        | 32 bits         |

# 3.2.1.1 AltiVec

AltiVec is the multimedia extension in Motorola PowerPC G4 processors. It is composed of a set of 128-bit registers that can be partitioned into 8, 16 and 32-bit integer partitions, and in 32-bit floating-point partitions. Most integer instructions are supported for all integer partition types, with a few exceptions. For example, *vec\_madds* (*multiply-high*) and *vec\_msum* (*multiply-add-pairs*) are supported only on 16-bit partitions.

AltiVec is programmed in an extended version of C that supports vector variables. All vectors are understood to be 128-bit long, so the type uniquely identifies the number of elements in the vector. For example:

```

vector char A;

vector int B;

```

means that A is a vector divided into 16 sections, each of which represents a signed 8-bit value, while B is a vector of 4 32-bit signed integer values. AltiVec also supports vector literals:

```

C = (vector char) (c)

D = (vector int) (c1, c2, c3, c4)

```

In this case, C results in a vector with all the elements equal to c, and D results in a vector whose four elements are equal to c1, c2, c3 and c4 respectively. Parallel operations are

executed using intrinsics. The intrinsics are overloaded for different vector types, so the following operations perform absolute value on partitions of different sizes:

```

vector char E, F;

vector int G, H;

F = vec_abs(E);

H = vec_abs(G);

```

Vectors can be loaded and stored in memory only at 16-byte aligned addresses. Unaligned accesses must be done through data rearrangement, using the permutation instruction. AltiVec's permutation instruction requires a vector of indices to define the permutation indices. Special instructions help set the permutation vector for data re-alignment:

```

perm_vector = vec_lvsl(0, pointer);

dst = vec_perm( vec_ld(0, ptr), vec_ld(0, ptr+1), perm_vector);

```

In this example, the intrinsic *vec\_lvs1* creates a permutation vector from the unaligned address, which is later used to re-align the data using the permutation intrinsic *vec\_perm*.

#### $3.2.1.2 \, MMX + SSE$

MMX is the first of a series of extensions to Pentium processors. MMX uses a set of 64-bit registers partitioned into 8, 16 and 32-bit integer sections. SSE (Streaming SIMD Extensions) is a set of instructions that are complementary to MMX. It adds some integer instructions on the same registers, and a new set of 128-bit registers partitioned into 32-bit floating-point sections. The MMX registers share resources with the scalar floating-point registers, so they cannot be used at the same time. A special EMMS instruction must be executed before and after using MMX and SSE integer instructions, unless no scalar floating-point operations can happen. The SSE floating-point registers do not contend with other resources.

There are two methods for programming this architecture. One is to use \_m64 and \_m128 types, which represent the integer and floating-point vector registers. The size and type of the partitions are determined by the operation intrinsics. For example:

```

_m64 A, B, C, D;

A = _mm_add_pi8(A, B)

C = _mm_add_pi16(C, D)

```

In this example A gets the addition of 8-bit sections, while C gets addition of 16-bit partitions. The other method of programming is to use C++ vector classes, which overload the standard C operators for vectors, and infer the type from the variable class. I use the first method of intrinsics in MMM declarations.

Many MMM and SSE instructions can take a memory location as a second argument, as in the following example:

```

_m64 A;

char *pB;

A = _mm_add_pi8(A, *pB);

```

There are no alignment restrictions for integer loads and stores in this architecture. Loads and stores for integer vectors are done by de-referencing pointers. Floating-point vector loads and stores do have different performance when the address is 16-byte aligned or not, so there are specific intrinsics to load and store floating-point vectors to aligned and unaligned addresses:

```

_m128 A;

A = _mm_load_ps(aligned_pointer);

A = _mm_loadu_ps(unaligned_pointer);

```

Memory accesses as second arguments to floating-point instructions are required to be 16-byte aligned.

#### 3.2.1.3 SSE2

Pentium 4 processors, in addition to MMX and SSE, support the SSE2 instruction set. SSE2 reuses the 128-bit registers defined in SSE, but can now divide them into 8, 16, 32 and 64-bit integer partitions, or in 32 and 64-bit floating point sections.

This architecture is programmed very similarly to MMX and SSE, except that the new register types are \_m1281 for integer, and \_m128d for double precision floating-point. Single-precision floating-point is supported the same way as in SSE, using the \_m128 type.

In SSE2 the integer vectors have the same alignment requirements as the floating-point vectors in SSE. Normal memory accesses are required to be at 16-byte aligned addresses. This is true for memory addresses as second arguments to operations. Unaligned loads and stores are supported through a special set of intrinsics:

```

_m128i A;

A = _mm_loadu_si128(pointer);

```

## 3.2.1.1 TriMedia TM1300

The TriMedia processor does not have a separate set of multimedia registers, but it does have several partitioned instructions that operate on the regular 32-bit registers. Vectors are declared as integer variables, and the operation intrinsics define the size and type of the partitions:

```

int A, B, C;

A = QUADAVG(B, C);

```

In this example, A gets the average of vectors B and C divided into 8-bit unsigned partitions. Vector loads and stores are restricted to be on 4-byte aligned addresses.

Unaligned loads must be emulated using two loads and shifts. Special funnel-shift instructions are provided to realign data:

```

int A;

A = FUNSHIFT1(*pA, *(pA+1));

```

This example loads two 32-bit words from the aligned address pA, and realigns them by concatenating the last 3 bytes of \*pA with the first byte of \*(pA+1).

#### 3.2.2 Definition of a Common Virtual Instruction Set

The next step was to define a virtual instruction set based on all of the selected targets. This virtual architecture is composed of vector registers as long as the longest target registers. In this case, it is 128-bit registers with 8, 16, and 32-bit integer partitions, and 32-bit floating point partitions. The virtual architecture can support shorter vectors (i.e. 64-bit vectors), but they map sub-optimally to 128-bit architectures, so their use is discouraged.

The virtual instruction set includes all operations that are common, or can be emulated efficiently on all the targets. Different MMM macros are defined for each combination of operations, input and output vector lengths and types. Other characteristics, like special handling of overflow, are also specified by each operation macro.

Virtual instructions can be defined in a way that the exact behavior under boundary conditions is undefined. For example, an addition operation may be defined to have unspecified behavior under overflow. This allows it to be mapped to target instructions that handle overflow differently (i.e. perform saturation, or modulo arithmetic), and thus provide for a common instruction that otherwise would not be available.

The virtual instruction set does not include operations that cannot be emulated efficiently on all targets. Therefore, there are instructions in some of the target architectures that are not available to MMM programs. An objective of this research is to determine how much performance is lost by not using these instructions. The virtual instruction set for the selected targets is discussed in Chapter 4, and the full definition appears in Appendix A.

# 3.2.3 Implementation of an MMM Library for each Target

Once a common virtual instruction was defined, it was possible to implement it for the different target architectures. I did not implement the full virtual instruction set, but only the part that was required by the selected example programs, described below. Appendix B shows the source code of the implementation of the MMM libraries for the four targets.

#### 3.2.4 Example Program Selection

I selected the following examples to be implemented in MMM: 8x8 integer IDCT, 16x16 integer L<sub>1</sub>-Distance, and 16x16 L<sub>1</sub>-Distance with interpolation. These kernels are used by MPEG2, MPEG4, and H.263+ video compression applications, and represent a large portion of their computational load. The 8x8 IDCT is also used in JPEG still-image compression. Hand-optimized versions of some of these kernels are available from the selected target processor vendors, and take advantage of the complex parallel operations available.

The three examples are tested in the context of an MPEG2 video encoder. The MPEG Software Simulation Group test model 5 [42] is used with a sequence of 704x576 outdoor images as input. The IDCT example is a direct replacement for the idct() function in the MPEG2 model. The L<sub>1</sub>-Distance examples replace portions of the dist1() function, corresponding to no interpolation, and both horizontal and vertical interpolation of 16x16 blocks. The dist1() function in the MPEG2 model also handles horizontal-only and vertical-

only interpolation, as well as 16x8 blocks, which are not of interest for this research. The MPEG2 model was modified to guarantee 16-byte alignment of the working image buffers, and to separate the dist1() function into various components, according to the block size and interpolation type.

## 3.2.4.1 8x8 IDCT

The IDCT works on 8x8 blocks of 16-bit signed integers. The interface is a function call with two pointers to 16-bit integers, one for the input and one for the output, which can possibly overlap:

The input block is stored in a contiguous piece of memory in row-major format, so elements of each row are stored in adjacent locations in memory. The output is stored in the same format as the input. Each input element can have values between –300 and 300 inclusive. The function is to compute the two-dimensional IDCT of the input, and meet the accuracy requirements specified in the IEEE 1180-1990 standard [41].

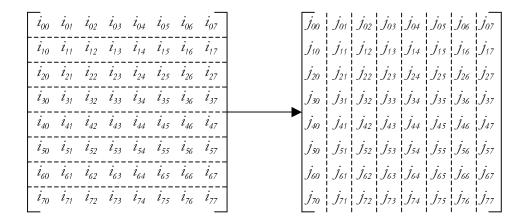

Two-dimensional IDCTs are usually implemented using a separable approach: first a one-dimensional IDCT is applied to each row, and then an IDCT is applied to each column.

This reduces the problem to the computation of one-dimensional IDCTs of length 8 over rows and columns of an 8x8 block. The 8-element IDCT is defined as:

$$x_{k} = \sum_{n=0}^{7} \cos \frac{\pi n (2k+1)}{16} c_{n} y_{n}$$

(3.1)

where  $c_0 = \frac{\sqrt{2}}{2}$  and  $c_n = \frac{1}{2}$  for n = 1,...,7. This can be expressed in matrix form as:

$$C_{8}^{-1} = \frac{1}{2} \begin{bmatrix} c_{4} & c_{1} & c_{2} & c_{3} & c_{4} & c_{5} & c_{6} & c_{7} \\ c_{4} & c_{3} & c_{6} & -c_{7} & -c_{4} & -c_{1} & -c_{2} & -c_{5} \\ c_{4} & c_{5} & -c_{6} & -c_{1} & -c_{4} & c_{7} & c_{2} & c_{3} \\ c_{4} & c_{7} & -c_{2} & -c_{5} & c_{4} & c_{3} & -c_{6} & -c_{1} \\ c_{4} & -c_{7} & -c_{2} & c_{5} & c_{4} & -c_{3} & -c_{6} & c_{1} \\ c_{4} & -c_{5} & -c_{6} & c_{1} & -c_{4} & -c_{7} & c_{2} & -c_{3} \\ c_{4} & -c_{3} & c_{6} & c_{7} & -c_{4} & c_{1} & -c_{2} & c_{5} \\ c_{4} & -c_{1} & c_{2} & -c_{3} & c_{4} & c_{5} & c_{6} & -c_{7} \end{bmatrix}$$

$$(3.2)$$

where  $c_k = \cos(\pi k/16)$ . Borrowing the notation from [44], this matrix can be decomposed as

$$C_8^{-1} = \frac{1}{2} A_8^{-1} M_8^{-1} P_8^{-1} \tag{3.3}$$

where

$$\boldsymbol{M}_{8}^{-1} = \begin{bmatrix} c_{4} & c_{2} & c_{4} & c_{6} & 0 & 0 & 0 & 0 \\ c_{4} & c_{6} & -c_{4} & -c_{2} & 0 & 0 & 0 & 0 \\ c_{4} & -c_{6} & -c_{4} & c_{2} & 0 & 0 & 0 & 0 \\ c_{4} & -c_{2} & c_{4} & -c_{6} & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & c_{1} & c_{3} & c_{5} & c_{7} \\ 0 & 0 & 0 & 0 & c_{3} & -c_{7} & -c_{1} & -c_{5} \\ 0 & 0 & 0 & 0 & c_{5} & -c_{1} & c_{7} & c_{3} \\ 0 & 0 & 0 & 0 & c_{7} & -c_{5} & c_{3} & -c_{1} \end{bmatrix}$$

This decomposition is the base of all fast IDCT algorithms. Most algorithms attempt to minimize the number of operations by further decomposing the operator  $M_8^{-1}$ . For example, a Chen IDCT [51] decomposes the even part (top left quadrant) of  $M_8^{-1}$  as:

$$\boldsymbol{M}_{4E}^{-1} = \begin{bmatrix} 1 & 0 & 0 & 1 \\ 0 & 1 & 1 & 0 \\ 0 & 1 & -1 & 0 \\ 1 & 0 & 0 & -1 \end{bmatrix} \begin{bmatrix} c_4 & c_4 & 0 & 0 \\ c_4 & -c_4 & 0 & 0 \\ 0 & 0 & c_6 & c_6 \\ 0 & 0 & c_2 & -c_2 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

(3.4)

And the odd part (bottom right quadrant) of  $M_8^{-1}$  is decomposed as:

$$\boldsymbol{M}_{4O}^{-1} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} c_7 & 0 & 0 & -c_1 \\ 0 & c_3 & -c_5 & 0 \\ 0 & c_5 & c_3 & 0 \\ c_1 & 0 & 0 & c_7 \end{bmatrix} \begin{bmatrix} 1 & 1 & 0 & 0 \\ 1 & -1 & 0 & 0 \\ 0 & 0 & -1 & 1 \\ 0 & 0 & 1 & -1 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & -c_4 & c_4 & 0 \\ 0 & c_4 & c_4 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

(3.5)

# 3.2.4.2 16x16 L<sub>1</sub>-Distance

The  $L_1$ -Distance kernels are used as part of Motion Estimation algorithms. A 16x16 image block is compared against several possible locations of a reference image in search for the location with the minimal distance between the two blocks. The distance is computed as the sum of absolute differences of all the corresponding pixels in the blocks:

$$L_1 Dist = \sum_{i=0}^{15} \sum_{j=0}^{15} \left| x_{i,j} - y_{i,j} \right|$$

(3.6)